Hiểu được sức mạnh của Latch S-R: Cổng vào các thiết bị điện tử hiện đại

Latches là các thiết bị kỹ thuật số đơn giản lưu trữ một chút thông tin và giữ giá trị đó cho đến khi nó nhận được tín hiệu đầu vào mới.Chúng được sử dụng trong các hệ thống kỹ thuật số để tạm thời giữ dữ liệu nhị phân.Các chốt có thể được thực hiện bằng cách sử dụng các loại cổng logic cơ bản khác nhau như và, hoặc không, NAND và cũng không có cổng.Bài viết này khám phá thiết kế, chức năng, biến thể và sử dụng của chốt S-R, nhấn mạnh vai trò tốt nhất của nó trong các thiết bị điện tử hiện đại và việc sử dụng nó trong các mạch thực tế và mô phỏng logic kỹ thuật số.

Danh mục

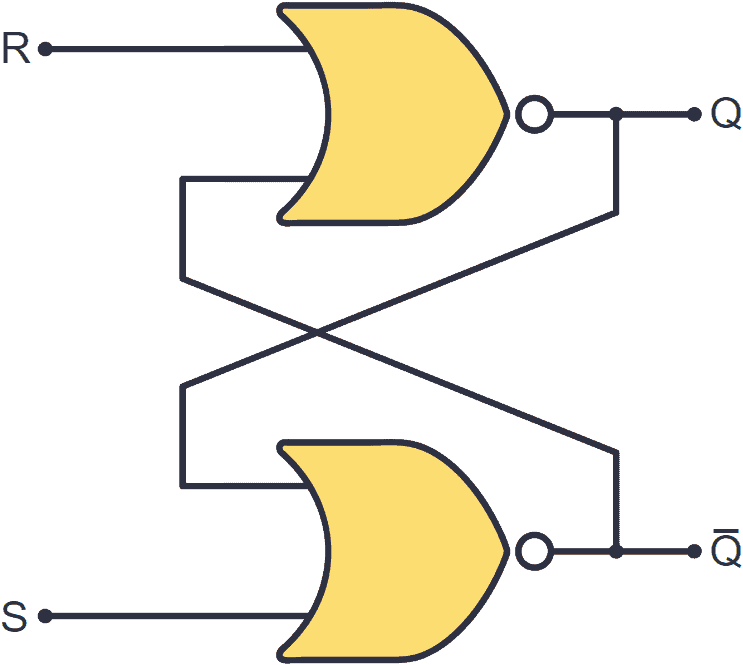

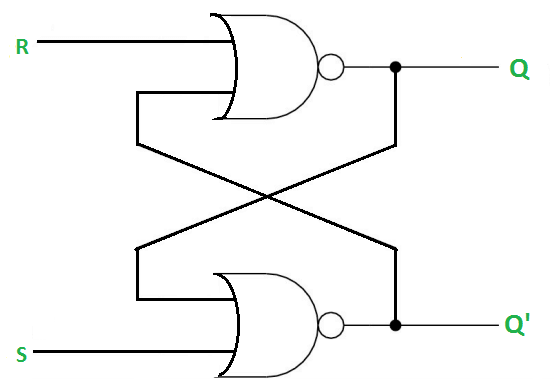

Hình 1: Sơ đồ mạch chốt S-R

Cấu trúc của chốt S-R

Latch S-R (bộ phận thiết lập), một nền tảng trong thiết bị điện tử kỹ thuật số, là một bộ đa biến có thể sử dụng được.Nó có khả năng duy trì một trong hai trạng thái khác biệt, ổn định vô thời hạn mà không có đầu vào bên ngoài.Chức năng này hiển thị SR chốt thành phần chính trong lưu trữ bộ nhớ và chuyển đổi các hoạt động trên các thiết bị điện tử khác nhau.

Về mặt cấu trúc, chốt SR bao gồm hai cổng kết nối cũng như cổng được sắp xếp trong một thiết kế vòng phản hồi.Sự sắp xếp cụ thể này có vấn đề vì nó cung cấp các điều kiện tiên quyết cho tính dễ thương.Mỗi đầu ra của cổng và cổng được kết nối trực tiếp với đầu vào của cái kia, tạo ra một vòng phản hồi liên tục làm nền tảng cho hoạt động của chốt.

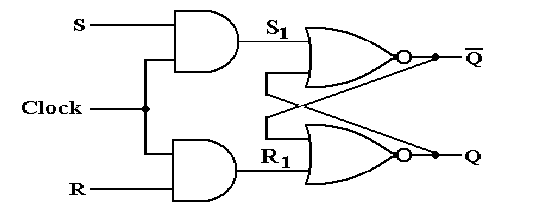

Hình 2: Latch S-R và tín hiệu đồng hồ (CLK)

Mở rộng trên thiết kế cơ bản, chốt SR Gated giới thiệu thêm, đầu vào: tín hiệu đồng hồ (CLK).Tăng cường này kết hợp đầu vào đồng hồ mang lại lớp điều khiển, tích hợp các hoạt động chốt vào các hệ thống yêu cầu đồng bộ hóa.Đồng bộ hóa này bắt buộc khi nó xác định các khoảnh khắc chính xác khi chốt có thể thay đổi trạng thái, được mô tả một cách khéo léo bằng thuật ngữ "gated".Việc bao gồm tín hiệu đồng hồ đảm bảo rằng các thay đổi đối với trạng thái đầu ra của chốt chỉ xảy ra trong pha đồng hồ hoạt động, thường ở cạnh tăng hoặc giảm của tín hiệu CLK.

Việc giới thiệu đầu vào CLK không chỉ bảo tồn các thuộc tính của chốt SR cơ bản mà còn phù hợp với hoạt động của nó với động lực học thời gian của các hệ thống kỹ thuật số lớn hơn.Mong muốn liên kết này để duy trì tính toàn vẹn của dữ liệu và đảm bảo rằng các chuyển đổi trạng thái xảy ra mà không bị trục trặc hoặc thay đổi ngoài ý muốn, đặc biệt là trong các cấu hình mạch phức tạp trong đó nhiều chốt có thể tương tác.Bằng cách kiểm soát khi chốt phản hồi các lệnh SET và đặt lại, hệ thống có thể tránh các vấn đề như điều kiện chủng tộc và các lỗi liên quan đến thời gian khác có thể phá vỡ sự ổn định và hiệu suất của hệ thống.

Trạng thái hoạt động của chốt S-R

Hoạt động của nó phụ thuộc vào đầu vào của hai tín hiệu điều khiển: SET (S) và Đặt lại (R).Ở đây, chúng tôi giải thích làm thế nào các đầu vào này ảnh hưởng đến các đầu ra và trạng thái của chốt SR.

Trường hợp 1: Đặt điều kiện

Khi đầu vào (các) đầu vào cao (1) và đầu vào đặt lại (r) thấp (0), chốt sẽ đi vào điều kiện đã đặt.Ở trạng thái này, cổng NAND được kết nối với đầu vào r sẽ tạo ra tín hiệu thấp do đầu vào cao từ S. Tín hiệu thấp này làm cho cổng NAND thứ hai xuất ra tín hiệu cao, đặt Q thành cao (1) và Q-Barđến thấp (0).Trạng thái này ổn định và sẽ giữ Q cao cho đến khi các đầu vào thay đổi, cho thấy khả năng lưu trữ trạng thái cao của chốt.

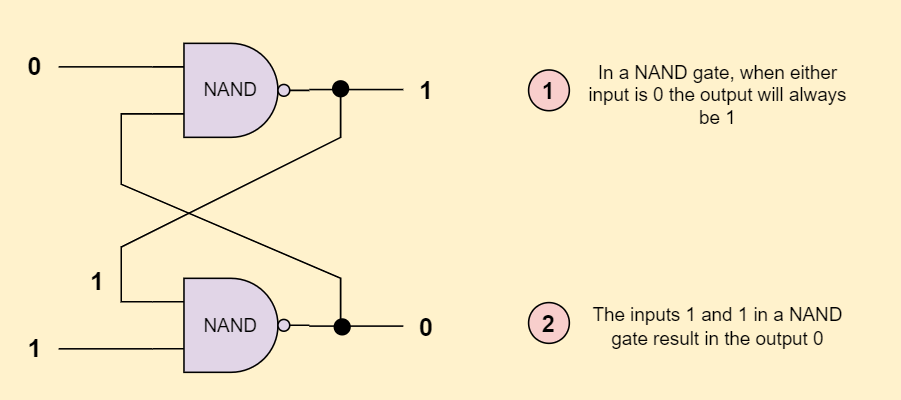

Hình 3: Trạng thái tập hợp

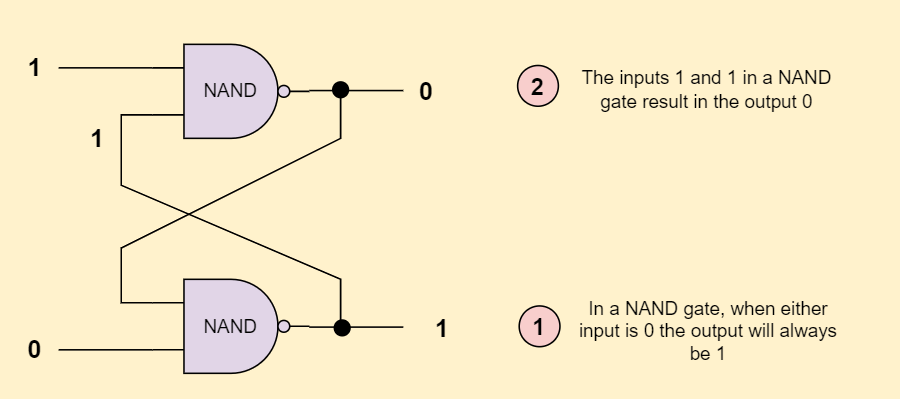

Trường hợp 2: Điều kiện đặt lại

Khi S thấp (0) và R cao (1), chốt đi vào điều kiện đặt lại.Ở đây, đầu vào cao trên R và đầu vào thấp trên S làm cho cổng NAND được kết nối với đầu ra R tín hiệu thấp.Tín hiệu thấp này đặt Q ở mức thấp (0) và Q-Bar đến cao (1), đặt lại hiệu quả chốt.Điều này cho thấy khả năng của chốt trở lại trạng thái thấp ổn định trong Q khi được cung cấp đúng đầu vào.

Hình 4: Trạng thái đặt lại

Trường hợp 3: Trạng thái không hợp lệ

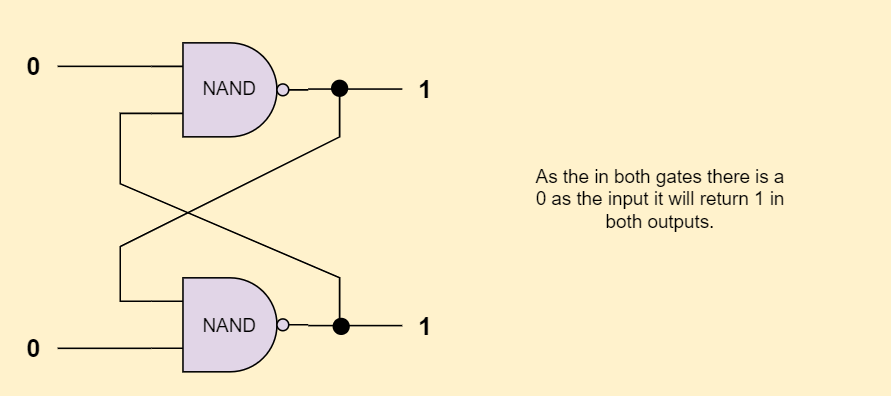

Nếu cả S và R đều thấp (0), cả hai đầu vào cho cổng NAND đều thấp, khiến cả đầu ra Q và Q-Bar sẽ lên cao.Trạng thái này được gọi là không hợp lệ hoặc bị cấm vì nó phá vỡ quy tắc cơ bản rằng Q và Q-Bar phải luôn luôn đối lập.Kịch bản này nêu bật giới hạn của chốt SR, nhấn mạnh tầm quan trọng của việc tránh các trạng thái không ổn định như vậy thông qua quản lý đầu vào thích hợp.

Hình 5: Trạng thái không hợp lệ

Trường hợp 4: Điều kiện giữ

Khi cả hai đầu vào đều cao (1), các đầu ra phụ thuộc vào trạng thái trước của chốt thay vì các đầu vào hiện tại.Điều này được gọi là điều kiện giữ, trong đó Q và Q-Bar vẫn không thay đổi, bảo tồn trạng thái hợp lệ cuối cùng của chốt.Đối với một số ứng dụng, điều quan trọng là có thể duy trì trạng thái chốt trong thời gian dài mà không cần sửa đổi, chẳng hạn như các ô lưu trữ bộ nhớ trong đó tính toàn vẹn dữ liệu có tầm quan trọng cao.

Hình 6: Trạng thái giữ

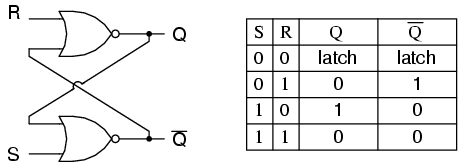

S-R chốt với một bảng sự thật

Bảng này không chỉ là một công cụ lý thuyết mà còn thực tế cho cả các nhà thiết kế mạch và sinh viên.Nó giúp họ thấy cách các chốt hoạt động trong nhiều điều kiện.Dưới đây, chúng tôi trình bày bảng sự thật toàn diện cho chốt SR, tiếp theo là giải thích và hiểu biết thực tế cho từng điều kiện.

|

S |

R |

Q. |

Q-Bar |

TÌNH TRẠNG |

|

0 |

0 |

1 |

1 |

Không hợp lệ |

|

0 |

1 |

0 |

1 |

Cài lại |

|

1 |

0 |

1 |

0 |

Bộ |

|

1 |

1 |

Q. |

Q-Bar |

Giữ |

Biểu đồ 1: SR

Bàn chân lý chốt

Giải thích về từng hàng

Điều kiện đặt (s = 1, r = 0): Hàng này cho thấy khi S cao và R thấp, Q được đặt thành cao (1) và Q-Bar ở mức thấp (0).Điều này phản ánh phản ứng của mạch đối với một lệnh đã đặt, lưu trữ hiệu quả '1'.

Điều kiện đặt lại (s = 0, r = 1): Ở đây, các đầu vào chỉ ra hoạt động đặt lại.Do đó, Q được đặt lại ở mức thấp (0) và Q-Bar được đặt thành cao (1).Trạng thái này thể hiện khả năng của chốt để trở lại '0'.

Điều kiện không hợp lệ (s = 0, r = 0): Cả hai đầu ra trở nên cao trong điều kiện này, thường được tránh vì nó dẫn đến cả hai đầu ra đều giống hệt nhau.Điều này có thể dẫn đến sự bất ổn hoặc hành vi không xác định trong chốt, vì nó vi phạm quy tắc rằng Q và Q-Bar phải luôn luôn đối lập.

Điều kiện giữ (s = 1, r = 1): Trong kịch bản này, chốt duy trì trạng thái trước đó, hiển thị khả năng giữ trạng thái tập hợp cuối cùng trừ khi được lệnh rõ ràng thay đổi.

Những hiểu biết và lời khuyên thực tế

Hiểu đầu ra: Luôn nhớ rằng Q và Q-Bar là bổ sung lý tưởng.Bất kỳ sai lệch nào so với quy tắc này (như đã thấy trong điều kiện không hợp lệ) đều biểu thị vấn đề hoặc cấu hình sai.

Tránh trạng thái không hợp lệ: Điều bắt buộc là các nhà thiết kế phải chăm sóc để ngăn chặn tình huống mà cả S và R đều thấp.Thực hiện logic hoặc khóa liên động bổ sung có thể giúp ngăn chặn trạng thái này.

Sử dụng điều kiện giữ: Điều kiện giữ có thể đặc biệt thuận tiện trong các ứng dụng yêu cầu bảo quản dữ liệu theo thời gian.Việc duy trì tính toàn vẹn của dữ liệu có thể phụ thuộc vào việc đảm bảo chốt không vô tình đi vào trạng thái tập hợp hoặc đặt lại.

Giải thích bảng sự thật: Khi thiết kế hoặc gỡ lỗi các mạch, tham chiếu bảng sự thật để dự đoán cách thay đổi đầu vào sẽ ảnh hưởng đến đầu ra, đặc biệt là trong các mạch phức tạp nơi sử dụng nhiều chốt.

Động lực chức năng của chốt S-R

Latch S-R (bộ phận đặt) chỉ hoạt động tốt nếu các đầu vào của nó được quản lý chính xác.Để hiểu cách thức hoạt động của nó, bạn cần biết các kết hợp đầu vào khác nhau ảnh hưởng đến đầu ra, Q và Q-Bar (ngược lại với Q).

Hình 7: Latch S-R

Nếu cả hai bộ (s) và đặt lại (r) được kích hoạt cùng một lúc (s = 1 và r = 1), chốt sẽ đi vào "trạng thái bị cấm", trong đó cả hai đầu ra, Q và Q-Bar, là 0.Đây là một vấn đề bởi vì thông thường, Q và Q-Bar nên đối lập.

Trong các điều kiện bình thường, để đặt chốt, bạn kích hoạt S (đặt S thành 1) và hủy kích hoạt R (đặt R thành 0).Điều này làm cho Q đi cao (1) và Q-Bar xuống thấp (0), hiển thị chốt có thể lưu trữ 1. Để đặt lại chốt, bạn kích hoạt R (đặt R thành 1) và hủy kích hoạt S (đặt S thành 0).Điều này làm cho Q xuống thấp (0) và Q-Bar lên cao (1), hiển thị chốt có thể tự xóa và lưu trữ 0.

Khi cả hai đầu vào bị hủy kích hoạt (s = 0 và r = 0), chốt giữ trạng thái cuối cùng của nó, được đặt hoặc đặt lại.Điều này là tốt để lưu trữ dữ liệu hoặc giữ trạng thái mà không cần đầu vào liên tục.

Điều kiện chủng tộc có thể làm phức tạp hoạt động của S-R Latch.Những lỗi này xảy ra khi các đầu ra phụ thuộc rất nhiều vào thời gian thay đổi đầu vào, dẫn đến kết quả không thể đoán trước nếu các đầu vào thay đổi gần như cùng một lúc.Để ngăn chặn điều này và đảm bảo chốt hoạt động đáng tin cậy, các cơ chế giảm thời gian thường được sử dụng.Những sự chậm trễ này đảm bảo một đầu vào kích hoạt sau khi người kia có thời gian để ổn định.Đối với chốt được sử dụng trong các mạch kỹ thuật số khi cần thời gian chính xác, nó phải thực hiện một cách nhất quán và duy trì đầu ra ổn định.Điều này được thực hiện bằng thời gian kiểm soát.

Sơ đồ logic của chốt S-R

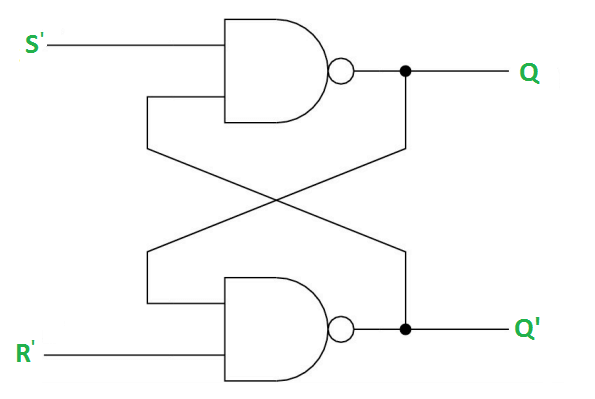

Latch SR là một mạch logic tuần tự cơ bản với hai cấu hình chính: cũng không hoặc cổng NAND.Mỗi thiết lập ảnh hưởng đến cách chốt hoạt động và phản hồi đầu vào, cho phép tùy chỉnh cho các ứng dụng điện tử khác nhau.

Hình 8: Sơ đồ logic đại diện cho chốt S-R sử dụng cổng NAND

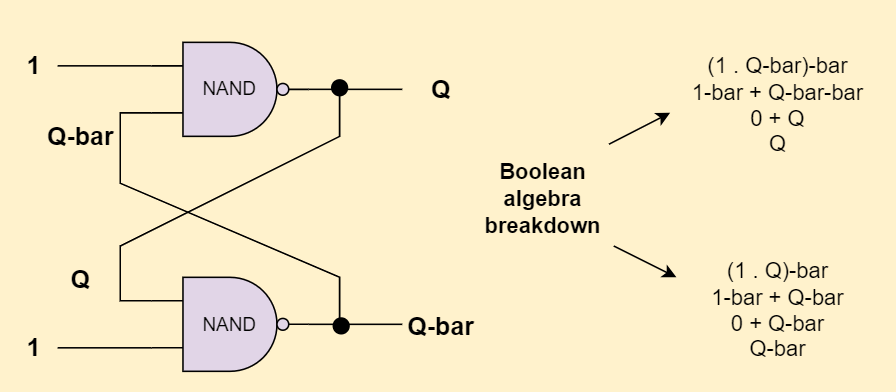

Việc thực hiện bằng Gates NAND

Khi xây dựng một chốt SR với cổng NAND, một vòng phản hồi được sử dụng để duy trì trạng thái của nó.Thiết lập này cho phép chốt giữ trạng thái trước đó khi cả đầu vào (S và R) đều thấp.Đầu ra của Gates NAND trừ khi cả hai đầu vào đều cao.Trạng thái của chốt thay đổi khi một đầu vào cao và cái còn lại thấp.Tốt nhất là tránh thiết lập cả S và R cao cùng một lúc vì điều này buộc cả hai đầu ra phải xuống thấp, dẫn đến trạng thái không xác định nơi các đầu ra không còn bổ sung.Quản lý đầu vào thích hợp là phải ngăn chặn sự bất ổn trong các chốt SR có trụ sở tại NAND.

Việc thực hiện bằng cách sử dụng các cổng cũng không

Sử dụng các cổng cũng như một chốt SR thay đổi các điều kiện hoạt động so với cổng NAND.Trong cấu hình này, chốt giữ trạng thái của nó khi cả hai đầu vào đều cao.Latch thay đổi trạng thái khi một đầu vào thấp và đầu còn lại cao.Cũng không chỉ đầu ra CAO nếu cả hai đầu vào đều thấp.Thiết lập này rất hữu ích trong các mạch trong đó trạng thái mặc định là có cả hai đầu ra thấp, đảm bảo đầu ra có thể dự đoán được trong các điều kiện đầu vào cao.Tuy nhiên, tốt nhất là tránh thiết lập cả đầu vào thấp cùng một lúc, vì điều này gây ra đầu ra mâu thuẫn và giảm độ tin cậy của chốt.

Hình 9: Sơ đồ logic đại diện cho chốt S-R sử dụng cổng NO

Mạch ví dụ

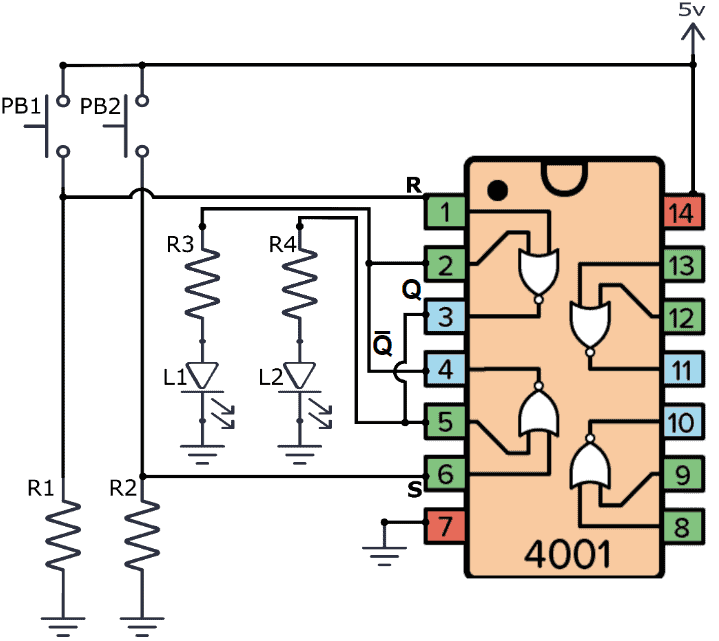

Khám phá cách các chốt SR hoạt động trong cuộc sống thực cho thấy tính hữu dụng của chúng.Một ví dụ điển hình là một mạch sử dụng chip CD4001, có bốn cổng cũng như cổng.Mạch này cho thấy cách các chốt SR có thể điều khiển các thiết bị như đèn LED với các hành động đơn giản như nhấn nút.

Trong ví dụ này, các cổng NOR trong chip CD4001 được thiết lập để tạo một chốt SR.Hai cổng được kết nối trong một vòng phản hồi để giữ trạng thái chốt.PushButtons được thêm vào mạch làm đầu vào cho SET và đặt lại.Nhấn một nút thay đổi trạng thái của đầu vào, thay đổi trạng thái chốt và trạng thái LED.Ví dụ: nhấn nút SET sáng lên đèn LED và nó vẫn được thắp sáng ngay cả sau khi nút được phát hành, cho thấy cách chốt có thể giữ trạng thái.

Để làm cho mạch tốt hơn, nhiều đèn LED có thể được thêm vào để hiển thị trạng thái đầu ra của cả Q và Q-Bar.Điều này giúp dễ dàng hơn để xem các chốt hoạt động như thế nào, rất hữu ích trong môi trường học tập.

Hình 10: chốt S-R sử dụng chip CD4001

Thực hiện mã

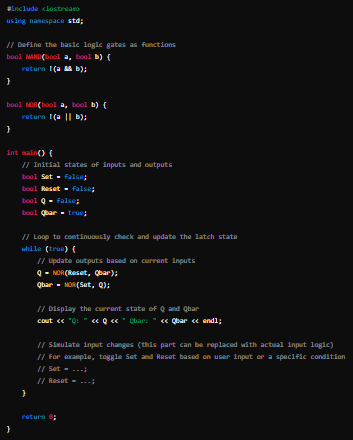

Dịch logic hoạt động của chốt SR thành phần mềm cho thấy cách thiết kế logic kỹ thuật số có thể hoạt động cả về phần cứng và mô phỏng ảo.Sử dụng ngôn ngữ lập trình như C ++ có hiệu quả vì nó hỗ trợ logic và kiểm soát phức tạp cần thiết để bắt chước các hành vi phần cứng.

Để tạo một chốt SR trong C ++, bạn bắt đầu bằng cách xác định các cổng logic cơ bản là các chức năng hoạt động giống như các phiên bản phần cứng của chúng.Chẳng hạn, một hàm cổng NAND sẽ trả về đối diện và hoạt động trên các đầu vào của nó.Tương tự, một hàm cổng NOR sẽ trả về đối diện với hoạt động hoặc hoạt động.Với các chức năng cơ bản này, bạn có thể mô hình hóa hành vi của SR chốt bằng cách tạo vòng lặp phản hồi giữa các chức năng cổng này, dựa trên sơ đồ mạch của chốt.

Mã thường sẽ có một vòng lặp liên tục kiểm tra các trạng thái của các đầu vào (đặt và đặt lại) và cập nhật các đầu ra (Q và Q-BAR) cho phù hợp.Các câu lệnh có điều kiện bên trong vòng lặp này xác định cách thay đổi đầu vào ảnh hưởng đến các đầu ra, bắt chước chặt chẽ hành vi vật lý của chốt SR.Ví dụ: nếu cả đầu vào đặt và đặt lại đều thấp, các đầu ra vẫn giữ nguyên.Nếu Set cao và đặt lại thấp, Q đầu ra sẽ trở nên cao và Q-Bar trở nên thấp, sao chép điều kiện đặt của chốt.

Đây là một ví dụ đơn giản về cách này có thể trông như thế nào trong mã:

Hình 11: Latch SR trong C ++

Mã này thiết lập một chốt SR đơn giản bằng cách sử dụng các cổng và liên tục kiểm tra và cập nhật trạng thái chốt dựa trên các đầu vào.

Các ứng dụng của chốt SR

Hệ thống điều khiển trong hoạt động của động cơ: Latch SR theo yêu cầu của các hệ thống để điều khiển động cơ.Sử dụng các công tắc nút bắt đầu và Stop (R) Pushbutton, chốt SR giữ một động cơ chạy ngay cả sau khi nút khởi động được giải phóng.Thiết lập này đảm bảo động cơ chạy liên tục cho đến khi dừng lại, tăng cường sự an toàn và thuận tiện.

Bộ nhớ và lưu trữ dữ liệu: Khi tạo các mạch bộ nhớ lớn hơn, chốt SR đóng vai trò vì nó có thể lưu trữ một chút dữ liệu.Nó duy trì dữ liệu ở trạng thái ổn định cho đến khi được cập nhật, hình thành cơ sở của các ô nhớ trong điện toán kỹ thuật số.

Kiểm soát và quản lý tín hiệu: Trong các ứng dụng tín hiệu điều khiển, các chốt SR giữ các bit cụ thể cho đến khi một số điều kiện nhất định được đáp ứng, đảm bảo trình tự và thời gian thích hợp trong các hoạt động.Độ chính xác trong xử lý tín hiệu và luồng dữ liệu phụ thuộc vào điều này.

Các mạch gỡ rối: Latch SR ổn định tín hiệu từ các công tắc và nút cơ học, ngăn chặn kích hoạt sai và lỗi do "nảy" khi nhấn công tắc.Điều này đặc biệt phù hợp trong các giao diện kỹ thuật số như bàn phím.

Các yếu tố nền tảng trong các hệ thống kỹ thuật số: Thiết kế của flip-flop và quầy, phù hợp với thời gian và trình tự trong thiết bị điện tử, phụ thuộc rất nhiều vào các chốt SR.Chúng cũng được sử dụng làm chốt xung để chuyển đổi trạng thái nhanh.

Các ứng dụng chuyên dụng: Trong các hệ thống không đồng bộ, các biến thể như chốt D được sử dụng để truyền dữ liệu an toàn và đáng tin cậy.Trong các hệ thống hai pha đồng bộ, các chốt dữ liệu làm giảm số lượng quá trình vận chuyển, cải thiện hiệu quả và giảm độ trễ.

Ý nghĩa rộng hơn trong thiết bị điện tử: Latches SR được sử dụng rộng rãi trong các mạch điện, đóng một phần trong bảo tồn năng lượng trong các thiết bị điện tử.Họ quản lý các trạng thái năng lượng ở mức chi tiết, góp phần vào hiệu quả năng lượng tổng thể của các hệ thống kỹ thuật số.

Phần kết luận

Các chốt S-R cho thấy tầm quan trọng của các cấu trúc logic đơn giản trong các hệ thống kỹ thuật số phức tạp.Bằng cách xem xét các thiết lập khác nhau của nó và cách nó hoạt động, chúng ta thấy rằng chốt S-R giữ cho dữ liệu ổn định và làm cho các hệ thống hiệu quả và đáng tin cậy.Nó có thể hoạt động trong các điều kiện khác nhau, được hiển thị bởi các bảng sự thật và sơ đồ logic, làm cho nó có thể thích ứng với một số ứng dụng, từ điều khiển động cơ đến các mạch kỹ thuật số cơ bản như dép xỏ ngón và quầy.Latch S-R phù hợp trong nhiều ứng dụng thực tế, chẳng hạn như các tế bào bộ nhớ trong máy tính và các mạch gỡ rối trong giao diện kỹ thuật số, tăng cường hiệu quả và giảm lỗi trong các thiết bị điện tử.Với các cơ chế phản hồi và quản lý tín hiệu đầu vào cẩn thận, chốt S-R rất tốt cho việc thiết kế các hệ thống kỹ thuật số đáng tin cậy và hiệu quả hơn.Nghiên cứu chức năng của nó thông qua mô phỏng phần mềm giúp kết nối các thiết bị điện tử lý thuyết với các ứng dụng trong thế giới thực, làm cho S-R chốt một chủ đề quan trọng cho cả các kỹ sư điện tử mới và có kinh nghiệm.

Câu hỏi thường gặp [Câu hỏi thường gặp]

1. Mục đích của chốt SR là gì?

Latch SR được sử dụng để lưu trữ một chút dữ liệu;Nó là một hình thức cơ bản của bộ nhớ trong các mạch kỹ thuật số.Chức năng chính của nó là giữ lại trạng thái của một chút cho đến khi nó được thay đổi bởi các tín hiệu đầu vào.

2. Latch SR hoạt động cao hay thấp?

Latch SR thường hoạt động cao, có nghĩa là nó đáp ứng với đầu vào cao (logic cấp 1).Khi các đầu vào S (SET) và R (đặt lại) cao, chúng sẽ kích hoạt các thay đổi trong đầu ra.

3. Nhược điểm với chốt SR là gì?

Một nhược điểm chính của chốt SR là tính nhạy cảm của nó đối với một điều kiện không hợp lệ trong đó cả đầu vào tập hợp và đặt lại đều cao đồng thời.Tình huống này dẫn đến một đầu ra không xác định, có thể dẫn đến hành vi không đáng tin cậy hoặc không thể đoán trước.

4. Các quy tắc cho chốt SR là gì?

Nếu S (SET) cao và R (Đặt lại) thấp, đầu ra Q được đặt thành cao.

Nếu R cao và S thấp, đầu ra Q được đặt lại ở mức thấp.

Nếu cả S và R đều thấp, đầu ra vẫn giữ trạng thái trước đó.

Nếu cả S và R đều cao, đầu ra không được xác định hoặc không hợp lệ.

5. Bộ nhớ trong chốt SR là gì?

Bộ nhớ trong chốt SR đề cập đến khả năng duy trì trạng thái đầu ra (cao hoặc thấp) vô thời hạn, cho đến khi nhận được đầu vào để thay đổi trạng thái.Điều này làm cho nó trở thành một thiết bị có thể sử dụng được, lý tưởng để lưu trữ bộ nhớ đơn giản.

6. Đầu ra của chốt SR là gì?

Latch SR có hai đầu ra, Q và Q '(Q-BAR).Q đại diện cho trạng thái hiện tại, trong khi Q 'là nghịch đảo của Q. Khi Q cao, Q' thấp và ngược lại.

7. Chúng ta sử dụng chốt ở đâu?

Khi cần lưu trữ dữ liệu ngắn hạn hoặc lưu giữ trạng thái, các chốt được sử dụng trong các loại ứng dụng khác nhau.Điều này bao gồm lưu trữ dữ liệu trong flip-flop, thanh ghi và đơn vị bộ nhớ, cũng như trong các hệ thống yêu cầu đồng bộ hóa dữ liệu và các chức năng giữ mạch.