Hiểu các tệp đầu ra của Bitgen cho cấu hình xilinx fpga

Hướng dẫn này khám phá các tệp đầu ra của Bitgen để định cấu hình các thiết bị xilinx.Các tệp này là chìa khóa để lập trình và vận hành các thiết bị trong khi cải thiện quy trình thiết kế.Từ các tệp bitstream đến các khóa nhật ký và mã mã hóa, mỗi loại phục vụ một mục đích cụ thể trong việc tối ưu hóa và bảo mật các cấu hình FPGA.Cho dù bạn đang khắc phục sự cố hoặc tinh chỉnh thiết kế, hướng dẫn này sẽ giúp bạn hiểu và sử dụng bitgen một cách hiệu quả để thiết lập FPGA.Danh mục

Tổng quan về tệp đầu ra

BitGen là một công cụ quan trọng để định cấu hình các thiết bị Xilinx, tạo ra một mảng các tệp đầu ra đa dạng để đảm bảo các thiết bị hoạt động đúng.Các tệp này không chỉ là các sản phẩm phụ kỹ thuật mà là các thành phần của quy trình công việc thiết kế FPGA thành công.Để tối đa hóa tiện ích của công cụ bitgen, bạn phải hiểu mục đích của các tệp này, cách chúng được tạo và các điều kiện ảnh hưởng đến thế hệ của chúng.Các tệp đầu ra của Bitgen, rơi vào các danh mục riêng biệt, mỗi loại phục vụ một vai trò cụ thể.Chẳng hạn, tệp bitStream lập trình FPGA, trong khi các tệp khác cung cấp cài đặt cấu hình, ghi nhật ký hoặc chi tiết gỡ lỗi.Nắm bắt các sắc thái của các tệp này cho phép khắc phục sự cố một cách hiệu quả, tinh chỉnh các thiết kế và tối ưu hóa hiệu suất của thiết bị.

Việc tạo các tệp này phụ thuộc vào các yếu tố như độ phức tạp thiết kế, sử dụng tài nguyên và các yêu cầu thiết bị cụ thể.Đôi khi, các tệp đầu ra có thể không đáp ứng mong đợi, yêu cầu dựa vào kinh nghiệm trước đó, thử và lỗi hoặc tài nguyên cộng đồng để xác định và giải quyết các vấn đề.Hơn nữa, các tệp đầu ra và quy trình thiết kế được kết nối sâu.Các thiết kế có cấu trúc tốt tạo ra các tệp đầu ra đáng tin cậy hơn và phân tích các tệp đó có thể cung cấp phản hồi có giá trị để cải thiện các thiết kế.Vòng phản hồi này tăng cường cả hiệu suất thiết bị và độ tin cậy thiết kế.Sử dụng Bitgen một cách hiệu quả không chỉ là các bước kỹ thuật, nó đòi hỏi một cách tiếp cận chu đáo kết hợp kiến thức kỹ thuật.Bằng cách xây dựng sự hiểu biết sâu sắc hơn về các tệp đầu ra của Bitgen, bạn có thể tiếp cận thiết kế và cấu hình của FPGA với sự tự tin và độ chính xác.

Các loại tệp và mục đích của chúng

Bitgen tạo ra nhiều loại tệp đầu ra, mỗi tệp được thiết kế cho một chức năng cụ thể trong thiết kế, cấu hình và triển khai của FPGA.Các tệp này giúp đảm bảo quy trình công việc hiệu quả và lập trình thiết bị chính xác.

.bit (tệp cấu hình nhị phân)

.BIT (Tệp cấu hình nhị phân) đóng vai trò là tệp chính để lập trình PPGA.Tệp nhị phân này chứa dữ liệu cấu hình và thông tin tiêu đề độc quyền cần thiết cho các công cụ tiếp theo như promgen và tác động.Nó được tạo theo mặc định trừ khi tùy chọn "-j" được chỉ định.Tầm quan trọng của nó nằm ở vai trò là đầu vào cốt lõi cho lập trình, đảm bảo FPGA hoạt động như dự định.

.RBT (tệp cấu hình ASCII)

Tệp cấu hình .RBT (ASCII) đóng vai trò là biểu diễn có thể đọc được của con người của tệp .bit.Được tạo khi tùy chọn "-B" được chọn, tệp này cho phép các nhà thiết kế dễ dàng diễn giải dữ liệu cấu hình.Nó rất hữu ích cho việc gỡ lỗi, tài liệu và hợp tác nhóm, vì nó cung cấp tính minh bạch trong quy trình cấu hình và đảm bảo rằng dữ liệu có thể truy cập và dễ hiểu cho tất cả các bên liên quan.

.BGN (Tệp nhật ký hoạt động)

.BGN (Tệp nhật ký hoạt động) đóng vai trò là nhật ký chi tiết của quy trình bitgen.Tệp này luôn được tạo và bao gồm thông tin như tham số dòng lệnh, cảnh báo và lỗi.Tầm quan trọng của nó nằm ở vai trò là một nguồn tài nguyên có giá trị để khắc phục sự cố và tinh chỉnh quy trình thiết kế.Bằng cách kiểm tra tệp này, bạn có thể xác định và giải quyết các vấn đề hiệu quả hơn, đảm bảo các hoạt động mượt mà và hiệu quả hơn.

.drc (Nhật ký kiểm tra quy tắc thiết kế)

Nhật ký kiểm tra quy tắc thiết kế (.drc) phục vụ một mục đích quan trọng bằng cách ghi lại các lỗi và cảnh báo được xác định trong quá trình kiểm tra quy tắc thiết kế.Nhật ký này được tạo theo mặc định trừ khi tùy chọn "-d" được sử dụng để vô hiệu hóa nó.Tuân thủ các quy tắc thiết kế là tốt để đảm bảo FPGA thực hiện như mong đợi, làm cho việc xem xét nhật ký này một bước trong quá trình thiết kế.Thường xuyên kiểm tra nhật ký .drc có thể giúp ngăn ngừa các lỗi thiết kế tốn kém và duy trì tính toàn vẹn của hệ thống tổng thể.

.msk (Tệp dữ liệu mặt nạ)

.MSK (Tệp dữ liệu mặt nạ) phục vụ mục đích thêm dữ liệu mặt nạ vào các lệnh cấu hình của tệp .bit.Được tạo bằng tùy chọn "-M", tệp này sử dụng các bit mặt nạ để chỉ định xem có cần xác minh khi giá trị 0 cho biết cần xác minh hay không và 1 cho biết không có xác minh.Điều quan trọng cần lưu ý là tệp .msk không phù hợp với lập trình thiết bị trực tiếp, tuy nhiên, nó đóng một vai trò trong việc đảm bảo tính toàn vẹn của cấu hình.

.ll (Tệp bố cục logic)

Tệp bố cục logic (.ll) đóng vai trò là tài nguyên để cung cấp thông tin chi tiết về việc sử dụng tài nguyên thiết kế.Được tạo bằng tùy chọn "-I", tệp này bao gồm các chi tiết toàn diện như vị trí bit, địa chỉ khung, độ lệch và chi tiết tài nguyên logic.Mục đích chính của nó là hỗ trợ tối ưu hóa các thiết kế bằng cách xác định các tắc nghẽn tiềm năng và phân tích sử dụng tài nguyên một cách hiệu quả.

.Nky (Tệp khóa mã hóa)

The .nky (Encryption Key File) serves as an important component in facilitating encryption for Virtex-II devices.Được tạo bằng tùy chọn bằng cách sử dụng tùy chọn "-g mã hóa: Có", tệp này chứa khóa mã hóa cần thiết cho các cấu hình thiết bị an toàn.Mục đích chính của nó là tăng cường bảo mật thiết kế bằng cách ngăn chặn truy cập trái phép vào các cấu hình FPGA, đảm bảo rằng các thiết kế nhạy cảm vẫn được bảo vệ.

.RBA (Tệp lệnh Readback - ASCII)

Tệp *.rba (Tệp lệnh Readback - ASCII) phục vụ một mục đích quan trọng trong xác thực cấu hình FPGA bằng cách chứa các lệnh readback và dữ liệu dự kiến tương ứng.Tệp này được tạo bằng tùy chọn "-g Readback" và được thiết kế để sử dụng với các thiết bị Virtex/-e và Spartan-II/E.Trường hợp sử dụng chính của nó là đảm bảo tính chính xác của các cấu hình FPGA bằng cách so sánh dữ liệu đọc lại từ thiết bị với kết quả dự kiến, làm cho nó trở thành một công cụ quan trọng trong quá trình xác thực.

.RBB (Tệp lệnh readback - nhị phân)

The .rbb (Readback Command File - Binary) serves as the binary equivalent of the .rba file.Nó được tạo trong các điều kiện tương tự như tệp .rba, cung cấp tùy chọn bổ sung để xác thực đọc lại.Tầm quan trọng của nó nằm ở tính linh hoạt mà nó cung cấp, vì nó hỗ trợ cả định dạng ASCII và nhị phân, phục vụ cho các yêu cầu xác nhận khác nhau.

.RBD (Tệp dữ liệu Readback)

.RBD (Tệp dữ liệu Readback) là loại tệp được thiết kế cụ thể để tập trung vào dữ liệu đọc lại dự kiến mà không bao gồm các lệnh.Nó được tạo bằng tùy chọn "-g Readback" và phục vụ vai trò trong việc hợp lý hóa các quy trình xác minh.Bằng cách cô lập dữ liệu dự kiến, nó đơn giản hóa so sánh và đảm bảo xác thực kết quả hiệu quả.

.MSD (Tệp xác minh mặt nạ)

.MSD (Tệp xác minh mặt nạ) phục vụ một mục đích quan trọng bằng cách cung cấp thông tin xác minh mặt nạ chi tiết.Tệp này chứa dữ liệu khung và filler trong khi cụ thể loại trừ các lệnh.Ý nghĩa chính của nó nằm ở việc giúp đảm bảo tính chính xác và đầy đủ của các cấu hình FPGA, làm cho nó trở thành một thành phần tuyệt vời trong quá trình xác minh.

.BIN (Tệp dữ liệu nhị phân)

.BIN (Tệp dữ liệu nhị phân) là một tệp nhị phân được sắp xếp hợp lý chỉ chứa dữ liệu cấu hình.Nó được tạo bằng tùy chọn bằng cách sử dụng tùy chọn "-g nhị phân: có" và loại trừ tiêu đề độc quyền được tìm thấy trong các tệp .bit.Điều này làm cho nó lý tưởng cho các trường hợp sử dụng như lập trình tự động hoặc các kịch bản yêu cầu chi phí dữ liệu tối thiểu.

Về chúng tôi

ALLELCO LIMITED

Đọc thêm

Yêu cầu nhanh chóng

Vui lòng gửi một yêu cầu, chúng tôi sẽ trả lời ngay lập tức.

VHDL: Hướng dẫn toàn diện về ngôn ngữ mô tả phần cứng

trên 2024/12/31

Làm thế nào EDA chuyển đổi quy trình thiết kế điện tử?

trên 2024/12/31

Bài viết phổ biến

-

Máy tính đặt hướng dẫn phức tạp: Làm thế nào họ thay đổi điện toán?

trên 8000/04/19 147782

-

Pinout và tính năng USB-C

trên 2000/04/19 112062

-

Sử dụng các nguyên thủy mô phỏng hợp nhất xilinx: Hướng dẫn toàn diện về thiết kế và mô phỏng FPGA

trên 1600/04/19 111352

-

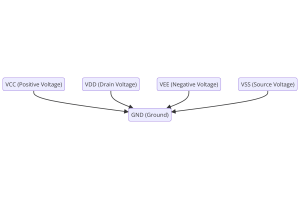

Điện áp nguồn trong điện tử: Ý nghĩa của VCC, VDD, VEE, VSS và GND

trên 0400/04/19 83819

-

Hướng dẫn kết nối RJ45: Pinout, hệ thống dây điện, loại cáp và sử dụng

trên 1970/01/1 79639

-

Hướng dẫn cuối cùng về mã màu dây trong các hệ thống điện hiện đại

Cách hệ thống điện của chúng tôi sử dụng màu sắc không chỉ dành cho ngoại hình.Mỗi màu dây hiện chỉ ra một chức năng cụ thể, giúp xác định và xử lý các thành phần điện một cách dễ dàng hơn trong qu...trên 1970/01/1 66999

-

Hướng dẫn van thanh lọc: Chức năng, triệu chứng, xét nghiệm và thay thế cho hiệu suất động cơ tối ưu

Van thanh lọc là một phần quan trọng của hệ thống xe hơi giúp giữ cho không khí sạch bằng cách quản lý hơi nhiên liệu trước khi chúng có thể thoát vào khí quyển.Điều này không chỉ giúp môi trường b...trên 1970/01/1 63124

-

Chất lượng (Q) Yếu tố: Phương trình và ứng dụng

Yếu tố chất lượng, hoặc 'Q', rất quan trọng khi kiểm tra mức độ cuộn cảm và bộ cộng hưởng hoạt động tốt trong các hệ thống điện tử sử dụng tần số vô tuyến (RF).'Q' đo lường mức độ một mạch giảm thi...trên 1970/01/1 63062

-

Đạt được hiệu suất cao nhất với Định lý Truyền công suất tối đa

Định lý truyền năng lượng tối đa giải thích cách năng lượng từ một nguồn, chẳng hạn như pin hoặc máy phát, chảy đến tải được kết nối.Nó cho thấy điều kiện chính xác trong đó tải nhận được nhiều năn...trên 1970/01/1 54097

-

Thông số kỹ thuật và khả năng tương thích của pin A23

Pin A23 là một pin nhỏ, hình xi lanh với điện áp cao.Cũng được gọi là 23A, 23AE hoặc MN21, nó chạy ở mức 12 volt và cao hơn nhiều so với pin AA hoặc AAA.Thiết kế đặc biệt của nó làm cho nó...trên 1970/01/1 52215