GAL20V8B-15LJN: Các tính năng, pinout, ứng dụng và hướng dẫn lập trình

GAL20V8B-15LJN là một thiết bị nổi bật được thiết kế cho nhiều tác vụ kỹ thuật số.Hướng dẫn này nhìn kỹ vào những gì GAL20V8B-15LJN có thể làm, tập trung vào tính linh hoạt và hiệu suất mạnh mẽ của nó trong các cách sử dụng khác nhau từ việc điều khiển máy đến cung cấp năng lượng cho các thiết bị hàng ngày.Chúng tôi sẽ bao gồm các tính năng chính của nó, cách thiết lập và cách lập trình nó, cung cấp một cái nhìn rõ ràng cho bất cứ ai muốn sử dụng các giải pháp logic nâng cao trong các dự án của họ.Danh mục

GAL20V8B-15LJN Mô tả

Các GAL20V8B-15LJN Từ mạng bán dẫn Lattice là một sự nổi bật trong họ thiết bị Gal® 20V8, được biết đến với hiệu quả và hoạt động tốc độ cao.Mô hình này được thiết kế bằng công nghệ E2CMOS, được tổ chức để tiêu thụ năng lượng thấp trong khi vẫn duy trì hiệu suất cao.Chủ yếu được sử dụng trong các ứng dụng logic kỹ thuật số như giải mã địa chỉ, giao diện thiết bị và thay thế logic, GAL20V8B-15LJN là linh hoạt và phù hợp với phổ rộng các ứng dụng logic có thể lập trình.GAL20V8B-15LJN bao gồm cấu hình 8 macrocell, tần số hoạt động tối đa là 62,5 MHz và độ trễ lan truyền chỉ 15 nano giây, đảm bảo hiệu suất nhanh chóng và đáng tin cậy.Nó hoạt động trên một nguồn cung cấp năng lượng 5V tiêu chuẩn và đi kèm trong gói PLCC (nhà cung cấp chip chì bằng nhựa).

Nếu bạn đang tìm kiếm một giải pháp logic lập trình đáng tin cậy và hiệu quả, GAL20V8B-15LJN là một lựa chọn tuyệt vời.Nó được xây dựng để cung cấp hiệu suất mạnh mẽ, làm cho nó trở thành một tùy chọn thông minh cho các doanh nghiệp nhằm nâng cấp công nghệ của họ.Nếu bạn đang xem xét một đơn đặt hàng số lượng lớn, đây là một cơ hội hoàn hảo để tối ưu hóa các ứng dụng của bạn và tận dụng tối đa cơ sở hạ tầng của bạn.

Cấu hình pin GAL20V8B-15LJN

Các GAL20V8B-15LJN là a Logic mảng chung (GAL) Thiết bị, một thiết bị logic có thể lập trình được sử dụng trong các ứng dụng logic kỹ thuật số khác nhau.Các Cấu hình pin theo a Bố cục gói kép 24 chân tiêu chuẩn (DIP), với đầu vào, đầu ra và chân điều khiển được xác định rõ ràng.

Trên bên trái của sơ đồ (chân 1-12), chúng ta chủ yếu thấy các chân đầu vào (i) cho phép thiết bị nhận tín hiệu từ các mạch bên ngoài.Chân 1 và một số chân khác (5, 7, 9 và 11) được chỉ định là đầu vào (I).Chân 6 và 22 được đánh dấu NC (không có kết nối), có nghĩa là chúng không được kết nối bằng điện với mạch bên trong.Chân GND (mặt đất) được định vị tại chân 12, đóng vai trò là điện áp tham chiếu cho thiết bị.

Trên bên phải .Các chân I/O này (18, 19, 21, 23, 25 và 26) cung cấp kết nối linh hoạt.Chân chế độ (chân 15) để xác định chế độ vận hành của thiết bị và chân VCC (nguồn điện) tại PIN 24 cung cấp điện áp cần thiết cho hoạt động phù hợp.

Tại đứng đầu Trong số các thiết bị, có các tín hiệu điều khiển bổ sung, bao gồm MCLK (đồng hồ chính, chân 2) và các chân NC bổ sung.Ghim của GAL20V8B cho phép thiết kế logic kỹ thuật số hiệu quả, làm cho nó trở thành một thành phần được sử dụng rộng rãi trong các mạch logic có thể lập trình.

Các mô hình CAD GAL20V8B-15LJN

Biểu tượng GAL20V8B-15LJN

Dấu chân GAL20V8B-15LJN

Các tính năng GAL20V8B-15LJN

• Độ trễ lan truyền: GAL20V8B-15LJN tự hào có độ trễ lan truyền tối đa 15 nano giây, có nghĩa là nó có thể xử lý các chuyển đổi tín hiệu nhanh và hoạt động hiệu quả trong các ứng dụng nhạy cảm với thời gian.

• Tần suất hoạt động: Nó hỗ trợ tần suất hoạt động tối đa là 62,5 MHz, tạo điều kiện xử lý nhanh chóng và đáp ứng trong các mạch logic kỹ thuật số phức tạp.

• Tiêu thụ năng lượng thấp: Thiết bị sử dụng công nghệ E2CMOS, một biến thể của CMO nhấn mạnh hiệu quả năng lượng.Công nghệ này đảm bảo rằng GAL20V8B-15LJN tiêu thụ ít năng lượng hơn, làm cho nó trở nên lý tưởng cho các ứng dụng cần hiệu quả năng lượng mà không cần hy sinh hiệu suất.

• Công nghệ di động E2 có thể lập trình lại: GAL20V8B-15LJN được trang bị các tế bào có thể xóa bằng điện, cho phép lập trình lại và cập nhật các chức năng logic khi cần thiết.Tính năng này cung cấp tính linh hoạt và khả năng thích ứng tuyệt vời trong việc thay đổi môi trường phần cứng hoặc cập nhật hệ thống.

• Logic đầu ra đa năng macrocells: Nó bao gồm 8 macrocell logic đầu ra có thể được lập trình riêng cho các hàm logic khác nhau, cho phép điều chỉnh thiết bị theo nhu cầu cụ thể.Các macrocell này hỗ trợ phân cực đầu ra có thể định cấu hình và có thể mô phỏng chức năng của các thiết bị PAL 24 chân, làm cho GAL20V8B-15LJN trở thành lựa chọn đa năng cho một loạt các ứng dụng kỹ thuật số.

• Tăng cường khả năng kiểm tra: Thiết bị có khả năng đặt lại trước và thiết lập lại cho tất cả các thanh ghi, đảm bảo khả năng kiểm tra chức năng 100%.Khía cạnh này là tuyệt vời để duy trì độ tin cậy và khả năng dự đoán trong các cài đặt hoạt động, đặc biệt là khi tính toàn vẹn và hiệu suất của hệ thống là quan trọng.

Sơ đồ khối GAL20V8B-15LJN

GAL20V8B-15LJN là một thiết bị logic mảng chung (GAL) bao gồm một thiết bị có thể lập trình và có thể lập trình (64 x 40), cho phép triển khai logic linh hoạt.Sơ đồ khối hiển thị các bản lập trình và mảng, đóng vai trò là công cụ logic chính trong đó các đầu vào và tín hiệu phản hồi được kết hợp một cách hợp lý.Ma trận lập trình này cho phép định cấu hình nhiều chức năng logic kết hợp và tuần tự, cung cấp tính linh hoạt trong thiết kế mạch kỹ thuật số.

Ở phía bên phải của sơ đồ, OLMC (các ô macro logic đầu ra) có thể nhìn thấy, mỗi tế bào kết nối với các đầu ra và mảng.Các tế bào vĩ mô này xác định hành vi của các chân đầu ra, cho dù chúng hoạt động như logic tổ hợp hoặc logic tuần tự với lưu trữ flip-flop.Ngoài ra, các đơn vị IMUX (bộ ghép kênh đầu vào) cho phép định tuyến tín hiệu nội bộ, tăng cường hơn nữa khả năng lập trình của thiết bị.I/OQ (chân đầu vào/đầu ra) biểu thị giao diện giữa thiết bị và các mạch bên ngoài, cho phép giao tiếp hai chiều tùy thuộc vào logic được cấu hình.

Sơ đồ đầu vào/đầu ra

Các sơ đồ tương đương đầu vào/đầu ra GAL20V8B-15LJN minh họa các đặc tính điện bên trong của các chân đầu vào và đầu ra của thiết bị.Các sơ đồ này nêu bật cách các thiết bị logic lập trình (PLD) quản lý các tín hiệu thông qua các mạch bảo vệ, kéo lên hoạt động và cơ chế kiểm soát ba trạng thái, đảm bảo hoạt động đáng tin cậy trong các mạch kỹ thuật số.

Các Đầu vào điển hình Sơ đồ cho thấy cấu trúc của một pin đầu vào, bao gồm các mạch bảo vệ ESD (phóng điện tĩnh điện) để ngăn ngừa thiệt hại từ các gai điện áp thoáng qua.Mạch kéo hoạt động đảm bảo rằng chân duy trì mức logic xác định khi không có tín hiệu bên ngoài nào điều khiển nó, ngăn chặn các trạng thái nổi có thể gây ra hành vi không thể đoán trước.Điện áp tham chiếu (VREF = 3.2V) đóng vai trò trong việc thiết lập ngưỡng để phát hiện logic cao hoặc trạng thái thấp.

Các Đầu ra điển hình Sơ đồ minh họa cấu trúc đầu ra, bao gồm cặp bóng bán dẫn kéo đẩy cho phép khả năng truyền động mạnh cho cả trạng thái logic cao và thấp.Chức năng điều khiển Tri-State cho phép pin đầu ra vào trạng thái chèn ép cao cho các thiết kế định hướng xe buýt trong đó nhiều thiết bị có chung kết nối.Đường dẫn phản hồi cung cấp kết nối nội bộ trở lại mảng logic, cho phép thiết bị theo dõi hoặc đồng bộ hóa trạng thái đầu ra với các hàm logic khác.Một mạch kéo hoạt động đảm bảo mức điện áp đáng tin cậy khi được yêu cầu.

GAL20V8B-15LJN được thiết kế cho các ứng dụng logic lập trình tốc độ cao, công suất thấp, với bảo vệ đầu vào mạnh mẽ, cấu hình đầu ra linh hoạt và đường dẫn phản hồi lập trình.Điều này làm cho nó phù hợp cho các thiết kế kỹ thuật số phức tạp yêu cầu tính toàn vẹn tín hiệu đáng tin cậy và các hoạt động logic có thể định cấu hình.

Thông số kỹ thuật GAL20V8B-15LJN

|

Kiểu |

Tham số |

|

Nhà sản xuất |

Tập đoàn bán dẫn mạng lưới |

|

Loạt |

GAL20V8B |

|

Bao bì |

Ống |

|

Trạng thái một phần |

Lỗi thời |

|

Loại lập trình |

Ee pld |

|

Tiểu loại |

Logic lập trình ICS |

|

Số lượng macrocells |

8 |

|

Tần số hoạt động tối đa |

62,5 MHz |

|

Độ trễ tuyên truyền - tối đa |

15 ns |

|

Điện áp cung cấp vận hành |

5 v |

|

HOẠT ĐỘNG CUNG CẤP HIỆN TẠI |

90 Ma |

|

Điện áp cung cấp - tối thiểu |

4,75 v |

|

Điện áp cung cấp - Tối đa |

5.25 v |

|

Nhiệt độ hoạt động tối thiểu |

0 ° C. |

|

Nhiệt độ hoạt động tối đa |

+75 ° C. |

|

Loại gắn kết |

Núi bề mặt |

|

Gói / trường hợp |

28-LCC (J-Lead) |

|

Gói thiết bị nhà cung cấp |

28-PLCC (11,51x11.51) |

|

Số sản phẩm cơ sở |

GAL20V8 |

|

Chiều cao |

3,68 mm |

|

Chiều dài |

11,5 mm |

|

Chiều rộng |

11,5 mm |

|

Trọng lượng đơn vị |

0,041719 oz |

Ứng dụng GAL20V8B-15LJN

Hệ thống nhúng

GAL20V8B-15LJN thường được sử dụng trong các hệ thống nhúng trong đó cần logic tùy chỉnh cho các chức năng điều khiển cụ thể.Bản chất lập trình của nó cho phép điều chỉnh thiết bị cho các quy trình lặp khác nhau, tăng cường chức năng và tích hợp với các thành phần hệ thống khác.

Hệ thống kiểm soát kỹ thuật số

Trong các hệ thống điều khiển kỹ thuật số, PLD này được sử dụng để triển khai logic phức tạp để điều khiển động cơ, giao tiếp với các cảm biến và tín hiệu xử lý.Khả năng xử lý logic điều khiển chi tiết của nó làm cho nó lý tưởng cho các ứng dụng yêu cầu kiểm soát và đáp ứng chính xác.

Giao diện giao tiếp

Thiết bị vượt trội trong việc quản lý các giao thức truyền thông, dữ liệu mã hóa và giải mã và kiểm soát các máy trạng thái.Nó thích nghi liền mạch với các tiêu chuẩn giao tiếp khác nhau, làm cho nó trở thành một lựa chọn linh hoạt cho các thiết bị viễn thông và mạng.

Thiết bị kiểm tra và đo lường

Đối với các ứng dụng kiểm tra và đo lường, GAL20V8B-15LJN cung cấp khả năng xử lý dữ liệu tùy chỉnh, định tuyến tín hiệu và logic điều khiển.Nó cho phép phát triển các giải pháp đo lường phù hợp yêu cầu các chức năng kiểm soát và xử lý dữ liệu cụ thể.

Điện tử ô tô

Trong lĩnh vực ô tô, PLD này nổi bật do thiết kế mạnh mẽ và bảo vệ phóng điện tĩnh điện (ESD) tuyệt vời.Các tính năng này đảm bảo hoạt động đáng tin cậy trong các điều kiện đòi hỏi điển hình trong môi trường ô tô.

Hệ thống điều khiển và tự động hóa công nghiệp

GAL20V8B-15LJN là công cụ tự động hóa công nghiệp, cung cấp logic cần thiết để kiểm soát các quy trình và máy móc công nghiệp phức tạp.Nó cho phép tự động hóa các tác vụ và tích hợp các hệ thống điều khiển, do đó tăng hiệu quả và độ tin cậy trong các hoạt động sản xuất.

Điện tử tiêu dùng

Trong điện tử tiêu dùng, thiết bị được sử dụng để tăng cường chức năng của các thiết bị hộ gia đình và cá nhân thông qua các giải pháp logic hiệu quả.Khả năng thực hiện nhiều chức năng logic về mặt kinh tế làm cho nó trở thành một lựa chọn phổ biến cho các nhà sản xuất sản phẩm tiêu dùng.

Máy trạng thái tùy chỉnh

PLD là lý tưởng để thiết kế các máy trạng thái tùy chỉnh trong các mạch kỹ thuật số, cải thiện hiệu quả của logic kiểm soát và giải trình tự vận hành.Ứng dụng này rất tuyệt vời trong các kịch bản trong đó các hành vi hoạt động cụ thể là cần thiết để quản lý các nhiệm vụ logic phức tạp một cách hiệu quả.

Lập trình GAL20V8B-15LJN

Lập trình GAL20V8B-15LJN, một thiết bị logic đa năng từ chất bán dẫn mạng, có thể được thực hiện một cách hiệu quả trong một vài bước chính, tận dụng một lập trình viên logic tương thích.Ban đầu, nhiệm vụ của bạn là thiết kế mạch logic bạn dự định thực hiện.Điều này đạt được bằng cách sử dụng ngôn ngữ mô tả phần cứng (HDL), với CUPL là một lựa chọn phổ biến do tính đơn giản, phù hợp cho các thiết bị GAL.Khi thiết kế logic của bạn được chỉ định, bước tiếp theo liên quan đến việc biên dịch thiết kế này thành tệp jedec (.jed) bằng phần mềm như wincupl.Tệp này chứa cấu hình cần thiết, được gọi là bản đồ cầu chì, để lập trình GAL.

Lập trình thực tế của GAL20V8B-15LJN yêu cầu một lập trình viên logic bán dẫn được phê duyệt mạng lưới, với TL866 là một mô hình thường được sử dụng do độ tin cậy và dễ sử dụng của nó.Bước này liên quan đến việc kết nối GAL20V8B-15LJN với lập trình viên theo các hướng dẫn được cung cấp, tải tệp Jedec vào phần mềm lập trình và bắt đầu chu kỳ lập trình.Chu kỳ này bao gồm việc xóa tự động của bất kỳ cấu hình trước đó trước khi lập trình logic mới vào thiết bị.Cuối cùng, một bước quan trọng là xác minh thiết bị được lập trình bằng cách kiểm tra nó trong mạch dự định để đảm bảo nó hoạt động chính xác, hoàn thành quy trình tích hợp với các yêu cầu ứng dụng cụ thể của bạn.

GAL20V8B-15LJN Đặt lại nguồn

Mạch thiết lập lại bật nguồn trong GAL20V8B-15LJN đảm bảo rằng tất cả các thanh ghi bên trong được khởi tạo đến trạng thái đã biết trong quá trình khởi động hệ thống.Khi công suất được áp dụng, điện áp VCC phải tăng đơn điệu mà không có biến động để ngăn chặn hành vi thất thường.Khi VCC đạt đến mức yêu cầu tối thiểu, các thanh ghi nội bộ sẽ đặt lại trong độ trễ tối đa là 1μs (TPR), đặt tất cả các đầu ra Q thành logic 0. Nếu các chân đầu ra đã đăng ký được bật, chúng sẽ mặc định là logic 1phân cực.Điều này đảm bảo một khởi tạo có thể dự đoán được, đơn giản hóa việc thiết kế các máy trạng thái và các mạch logic tuần tự.

Để đảm bảo thiết lập lại hợp lệ, đầu vào đồng hồ (CLK) phải được giữ ở mức TTL tĩnh trong quá trình bật nguồn.Thiết bị không nên được đồng hồ cho đến khi tất cả thời gian thiết lập đường dẫn đầu vào và phản hồi được đáp ứng, như được hiển thị trong sơ đồ.Đồng hồ phải tuân thủ các yêu cầu về độ rộng xung tối thiểu trước khi bắt đầu hoạt động bình thường.Bằng cách duy trì các điều kiện này, cơ chế thiết lập lại tăng sức mạnh đảm bảo rằng thiết bị logic bắt đầu ở trạng thái ổn định và được xác định rõ, ngăn chặn sự chuyển tiếp ngoài ý muốn hoặc các vấn đề về khả năng di chuyển trong các mạch kỹ thuật số.

GAL20V8B-15LJN Các bộ phận tương tự

GAL20V8B-15LJN Ưu điểm

Tăng cường tính linh hoạt thiết kế

GAL20V8B-15LJN được thiết kế với kiến trúc đa năng cho phép các macrocell logic đầu ra (OLMC) được cấu hình của người dùng.Tính linh hoạt này hỗ trợ một loạt các ứng dụng và tùy chỉnh, cho phép tối ưu hóa thiết bị logic cho các tác vụ và chức năng cụ thể mà không có các ràng buộc liên quan đến các thiết kế kém linh hoạt hơn.

Giảm tiêu thụ năng lượng

Sử dụng công nghệ CMOS nâng cao của Ultramos®, GAL20V8B-15LJN giảm 50% đến 75% tiêu thụ điện năng so với các thiết bị logic lưỡng cực truyền thống.Điều này làm cho nó trở thành một tùy chọn thân thiện với môi trường cũng giảm thiểu sản lượng nhiệt và tăng cường tuổi thọ của thiết bị.Dòng cung cấp điển hình thấp hơn đáng kể, với 75 mA cho các phiên bản năng lượng thấp tiêu chuẩn và thậm chí thấp hơn ở 45 mA cho các phiên bản cấp một phần tư, đảm bảo hiệu quả năng lượng trong môi trường có nhu cầu cao.

Bảo vệ ESD mạnh mẽ

Thiết bị này kết hợp các cơ chế bảo vệ phóng điện tĩnh điện mạnh (ESD), để duy trì sự ổn định và độ tin cậy hoạt động trong môi trường dễ bị xả tĩnh.Sự bảo vệ như vậy là tốt trong các ngành công nghiệp như ô tô và tự động hóa công nghiệp, nơi các thành phần điện tử có thể phải chịu các điều kiện nghiêm ngặt và nơi ESD có thể dẫn đến lỗi thiết bị hoặc hành vi thất thường.

Nhà sản xuất GAL20V8B-15LJN

Tập đoàn bán dẫn Lattice là một nhà lãnh đạo toàn cầu trong các giải pháp kết nối thông minh.Được biết đến với các thiết bị logic lập trình năng lượng thấp, mạng lưới phục vụ chủ yếu cho thị trường tiêu dùng, truyền thông và công nghiệp.Phạm vi sản phẩm sáng tạo của công ty bao gồm FPGA (mảng cổng lập trình hiện trường), CPLD (thiết bị logic lập trình phức tạp) và các thiết bị quản lý năng lượng, không thể thiếu đối với các ứng dụng thông minh yêu cầu phản hồi nhanh chóng.Chất bán dẫn Lattice khác biệt trong thị trường công nghệ cạnh tranh với trọng tâm là các giải pháp năng lượng thấp, quy mô nhỏ và hiệu suất cao.Các thuộc tính này làm cho các sản phẩm của nó trở nên lý tưởng để cho phép công nghệ trong các lĩnh vực như cơ sở hạ tầng mạng, điện toán cạnh và các thiết bị IoT thông minh.Lattice đã xây dựng danh tiếng cung cấp các giải pháp tùy chỉnh đáp ứng nhu cầu cụ thể, được hỗ trợ bởi các công cụ phần mềm toàn diện và môi trường phát triển hợp lý hóa thiết kế và triển khai sản phẩm.

Phần kết luận

GAL20V8B-15LJN từ chất bán dẫn Lattice là một thiết bị hàng đầu đáp ứng nhu cầu đòi hỏi của các hệ thống kỹ thuật số hiện đại với hiệu suất nhanh, thiết kế tiết kiệm năng lượng và các tùy chọn lập trình đa năng.Thiết bị này được xây dựng để giải quyết các thách thức phức tạp trong một loạt các cài đặt, từ các hệ thống công nghiệp lớn đến thiết bị điện tử cá nhân, khiến nó trở thành một lựa chọn vững chắc để xây dựng các giải pháp kỹ thuật số tiên tiến.Hướng dẫn này đã giải thích các chi tiết kỹ thuật và lợi ích của GAL20V8B-15LJN, cũng như cách sử dụng nó trong các lĩnh vực khác nhau, cho thấy tầm quan trọng của nó trong việc cải thiện các thiết lập kỹ thuật số ở khắp mọi nơi.

Biểu dữ liệu PDF

GAL20V8B-15LJN DATASHEETS:

Về chúng tôi

ALLELCO LIMITED

Đọc thêm

Yêu cầu nhanh chóng

Vui lòng gửi một yêu cầu, chúng tôi sẽ trả lời ngay lập tức.

Các câu hỏi thường gặp [FAQ]

1. GAL20V8B-15LJN có thể được lập trình để hỗ trợ các hệ thống kế thừa không?

Đúng.GAL20V8B-15LJN được thiết kế với tính linh hoạt trong tâm trí, có khả năng được lập trình để giao diện với cả hệ thống hiện đại và di sản.Logic có thể lập trình của nó cho phép một loạt các cấu hình tùy chỉnh có thể được điều chỉnh để đáp ứng các yêu cầu di sản cụ thể.

2. Những công cụ và phần mềm lập trình nào tương thích với GAL20V8B-15LJN?

GAL20V8B-15LJN tương thích với một loạt các công cụ và phần mềm lập trình, bao gồm Wincupl, Lattice Diamond và các công cụ của bên thứ ba hỗ trợ các tệp Jedec.Khả năng tương thích này đảm bảo tích hợp liền mạch vào quy trình phát triển hiện tại của bạn.

3. Làm thế nào để GAL20V8B-15LJN xử lý các dao động và tăng sức mạnh?

GAL20V8B-15LJN được xây dựng với các tính năng quản lý năng lượng mạnh mẽ để bảo vệ chống lại sự biến động và tăng, đảm bảo hoạt động ổn định ngay cả trong môi trường có nguồn cung cấp năng lượng không ổn định.

4. GAL20V8B-15LJN có thể được sử dụng trong môi trường nhiệt độ cao không?

Có, GAL20V8B-15LJN được thiết kế để hoạt động hiệu quả trong một phạm vi nhiệt độ rộng.Độ ổn định nhiệt cao của nó làm cho nó phù hợp để sử dụng trong môi trường công nghiệp nhiệt độ cao mà không ảnh hưởng đến hiệu suất.

5. Các ứng dụng phổ biến nhất của GAL20V8B-15LJN trong môi trường công nghiệp là gì?

Trong các thiết lập công nghiệp, GAL20V8B-15LJN thường được sử dụng để điều khiển máy, thiết bị thử nghiệm tự động và giám sát hệ thống do hiệu suất đáng tin cậy và khả năng lập trình linh hoạt của nó.

LFXP2-8E-5QN208C PPGA: Tương đương, tính năng, ứng dụng và lợi thế

trên 2025/02/11

Cách điện trở máy thổi điều khiển luồng không khí xe hơi của bạn

trên 2025/02/11

Bài viết phổ biến

-

Máy tính đặt hướng dẫn phức tạp: Làm thế nào họ thay đổi điện toán?

trên 8000/04/18 147776

-

Pinout và tính năng USB-C

trên 2000/04/18 112019

-

Sử dụng các nguyên thủy mô phỏng hợp nhất xilinx: Hướng dẫn toàn diện về thiết kế và mô phỏng FPGA

trên 1600/04/18 111351

-

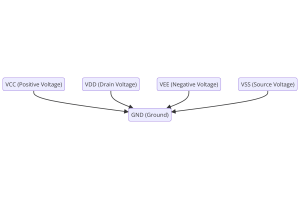

Điện áp nguồn trong điện tử: Ý nghĩa của VCC, VDD, VEE, VSS và GND

trên 0400/04/18 83777

-

Hướng dẫn kết nối RJ45: Pinout, hệ thống dây điện, loại cáp và sử dụng

trên 1970/01/1 79575

-

Hướng dẫn cuối cùng về mã màu dây trong các hệ thống điện hiện đại

Cách hệ thống điện của chúng tôi sử dụng màu sắc không chỉ dành cho ngoại hình.Mỗi màu dây hiện chỉ ra một chức năng cụ thể, giúp xác định và xử lý các thành phần điện một cách dễ dàng hơn trong qu...trên 1970/01/1 66964

-

Hướng dẫn van thanh lọc: Chức năng, triệu chứng, xét nghiệm và thay thế cho hiệu suất động cơ tối ưu

Van thanh lọc là một phần quan trọng của hệ thống xe hơi giúp giữ cho không khí sạch bằng cách quản lý hơi nhiên liệu trước khi chúng có thể thoát vào khí quyển.Điều này không chỉ giúp môi trường b...trên 1970/01/1 63104

-

Chất lượng (Q) Yếu tố: Phương trình và ứng dụng

Yếu tố chất lượng, hoặc 'Q', rất quan trọng khi kiểm tra mức độ cuộn cảm và bộ cộng hưởng hoạt động tốt trong các hệ thống điện tử sử dụng tần số vô tuyến (RF).'Q' đo lường mức độ một mạch giảm thi...trên 1970/01/1 63041

-

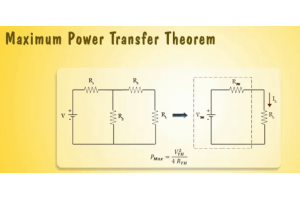

Đạt được hiệu suất cao nhất với Định lý Truyền công suất tối đa

Định lý truyền năng lượng tối đa giải thích cách năng lượng từ một nguồn, chẳng hạn như pin hoặc máy phát, chảy đến tải được kết nối.Nó cho thấy điều kiện chính xác trong đó tải nhận được nhiều năn...trên 1970/01/1 54097

-

Thông số kỹ thuật và khả năng tương thích của pin A23

Pin A23 là một pin nhỏ, hình xi lanh với điện áp cao.Cũng được gọi là 23A, 23AE hoặc MN21, nó chạy ở mức 12 volt và cao hơn nhiều so với pin AA hoặc AAA.Thiết kế đặc biệt của nó làm cho nó...trên 1970/01/1 52189