EPM7064STC100-7 CPLD: Các tính năng, ứng dụng và hướng dẫn lập trình trong hệ thống

EPM7064STC100-7 là một chip mạnh mẽ từ loạt MAX® 7000S của Intel, được thiết kế để xử lý các tác vụ phức tạp trong các thiết bị điện tử.Hướng dẫn này thảo luận về các tính năng chính và việc sử dụng của EPM7064STC100-7, nhấn mạnh khả năng được lập trình lại dễ dàng, hoạt động nhanh và thiết kế linh hoạt của nó.Lý tưởng cho nhiều công nghệ khác nhau, từ các thiết bị nhỏ đến máy công nghiệp lớn, con chip này là một phần quan trọng để xây dựng các mạch kỹ thuật số tiên tiến.Danh mục

EPM7064STC100-7 Mô tả

Các EPM7064STC100-7 là một thiết bị logic có thể lập trình phức tạp (CPLD) từ sê -ri MAX® 7000S của Intel.Nó có 64 macrocell và 1.250 cổng, giúp xây dựng các mạch kỹ thuật số phức tạp.Chip này chạy ở tốc độ tối đa 166,7 MHz, với độ trễ tín hiệu là 7,5 nano giây (NS).Nó có 68 chân đầu vào/đầu ra (I/O) hoạt động với logic 3,3V và 5V, giúp dễ sử dụng trong các mạch khác nhau.Một tính năng chính là khả năng lập trình trong hệ thống 5.0V của nó (ISP) thông qua giao diện JTAG (IEEE 1149.1).Điều này có nghĩa là bạn có thể lập trình lại nó mà không cần loại bỏ nó khỏi mạch, làm cho việc kiểm tra và cập nhật dễ dàng hơn.Nó đi kèm trong một gói bốn phẳng mỏng 100 chân (TQFP), đây là một gói nhỏ gọn, bề mặt.CPLD này được sử dụng trong các hệ thống nhúng, xử lý tín hiệu số, thiết bị truyền thông và tự động hóa công nghiệp.

Chúng tôi cung cấp các thành phần chất lượng cao và dịch vụ tùy chỉnh, vì vậy tốt nhất nên đặt hàng số lượng lớn của bạn với chúng tôi cho các giải pháp CPLD đáng tin cậy.

Các tính năng EPM7064STC100-7

• Logic mật độ cao: EPM7064STC100-7 được thiết kế với 64 macrocell và 1.250 cổng có thể sử dụng, làm cho nó rất phù hợp để thực hiện các chức năng logic phức tạp trong các mạch kỹ thuật số.Kiến trúc mật độ cao này cho phép tạo ra các thiết kế logic phức tạp trong khi duy trì hiệu quả trong các hoạt động logic lập trình.Cấu trúc macrocell được tối ưu hóa tốt đảm bảo sử dụng hiệu quả các tài nguyên có sẵn, hỗ trợ triển khai logic kết hợp và tuần tự nâng cao.

• Hiệu suất nhanh: Được xây dựng để xử lý tốc độ cao, EPM7064STC100-7 hoạt động với tần số nội bộ tối đa là 166,7 MHz, cho phép thực hiện nhanh chóng các hàm logic.Độ trễ lan truyền của nó là 7,5 ns đảm bảo độ trễ tối thiểu.Khả năng chuyển đổi nhanh chóng này giúp tăng cường khả năng xử lý dữ liệu tốc độ cao, điều hòa tín hiệu và điều khiển các tác vụ một cách hiệu quả, khiến nó trở thành một lựa chọn đáng tin cậy cho các hệ thống kỹ thuật số yêu cầu.

• I/O đa năng: Với 68 chân đầu vào/đầu ra có thể lập trình, EPM7064STC100-7 cung cấp tính linh hoạt đặc biệt để tích hợp vào các thiết kế mạch khác nhau.Hỗ trợ cả hai mức logic 3,3V và 5V, nó cho phép tương thích liền mạch với các điện áp hệ thống khác nhau, loại bỏ sự cần thiết phải có bộ chuyển số điện áp bổ sung.Khả năng thích ứng này làm cho nó phù hợp với các ứng dụng trong môi trường điện áp hỗn hợp, đảm bảo khả năng ứng dụng rộng trên các hệ thống nhúng, điều khiển công nghiệp và mạng truyền thông.

• Khả năng lập trình trong hệ thống (ISP): Một trong những ưu điểm của EPM7064STC100-7 là lập trình trong hệ thống 5.0V của nó (ISP), được tạo điều kiện thông qua IEEE STD.Giao diện 1149.1 JTAG.Tính năng này cho phép lập trình lại và sửa đổi các chức năng logic mà không cần giảm bớt hoặc loại bỏ vật lý thiết bị, đơn giản hóa việc bảo trì, gỡ lỗi và phát triển lặp lại.Khả năng ISP làm giảm thời gian chết và tăng cường tính linh hoạt của các bản cập nhật chương trình cơ sở, làm cho nó trở nên vô giá đối với các thiết kế kỹ thuật số động và có thể cấu hình lại.

Các mô hình CAD EPM7064STC100-7

Biểu tượng EPM7064STC100-7

Dấu chân EPM7064STC100-7

Mô hình 3D EPM7064STC100-7

EPM7064STC100-7 Sơ đồ khối

Các EPM7064STC100-7 Sơ đồ khối cho thấy cách các phần tử logic của chip được kết nối và kiểm soát.Nó có bốn khối mảng logic (phòng thí nghiệm), được gắn nhãn A, B, C và D, mỗi khối chứa 16 macrocells.Các macrocell này thực hiện các hàm logic và chúng kết nối thông qua một mảng kết nối có thể lập trình (PIA), cho phép định tuyến tín hiệu linh hoạt.Mỗi phòng thí nghiệm được liên kết với một khối điều khiển I/O, xử lý tối đa 16 chân đầu vào/đầu ra trên mỗi phòng thí nghiệm.Sơ đồ cũng cho thấy các tín hiệu điều khiển toàn cầu (GCLK1, GCLK2, OE1 và GCLRN) giúp quản lý các chức năng đồng hồ và đặt lại các chức năng cho chip.Một số cổng logic xử lý các tín hiệu này trước khi chúng đạt đến các phần khác nhau của hệ thống.Thiết kế của EPM7064STC100-7 cho phép nó được sử dụng trong các ứng dụng logic lập trình khác nhau, chẳng hạn như máy trạng thái, giải mã địa chỉ và các mạch kỹ thuật số tùy chỉnh khác.Các kết nối linh hoạt của nó đảm bảo lưu lượng tín hiệu hiệu quả và hoạt động đáng tin cậy.

Thông số kỹ thuật EPM7064STC100-7

|

Kiểu |

Tham số |

|

Nhà sản xuất |

Altera/Intel |

|

Loạt |

Max® 7000s |

|

Bao bì |

Khay |

|

Trạng thái một phần |

Lỗi thời |

|

Loại lập trình |

Trong lập trình hệ thống |

|

Thời gian trễ TPD (1) Tối đa |

7,5 ns |

|

Cung cấp điện áp - nội bộ |

4,75V ~ 5,25V |

|

Số lượng phần tử/khối logic |

4 |

|

Số lượng macrocells |

64 |

|

Số lượng cổng |

1250 |

|

Số lượng I/O. |

68 |

|

Nhiệt độ hoạt động |

0 ° C ~ 70 ° C (TA) |

|

Loại gắn kết |

Núi bề mặt |

|

Gói / trường hợp |

100-TQFP |

|

Gói thiết bị nhà cung cấp |

100-TQFP (14x14) |

|

Số sản phẩm cơ sở |

EPM7064 |

Trình tự lập trình trong hệ thống (ISP) EPM70644STC100-7

EPM7064STC100-7, một phần của họ CPLD tối đa 7000S, theo trình tự lập trình trong hệ thống (ISP) sáu giai đoạn để đảm bảo cấu hình chính xác.Quá trình này cho phép bạn lập trình thiết bị mà không cần tháo nó khỏi bảng mạch.Quá trình ISP bao gồm các hướng dẫn, địa chỉ và dữ liệu chuyển đổi thông qua mã PIN TDI (dữ liệu thử nghiệm trong) trong khi truy xuất các phản hồi thông qua mã PIN TDO (Dữ liệu thử nghiệm).

Giai đoạn đầu tiên, Nhập ISP, đảm bảo rằng các chân I/O chuyển tiếp một cách trơn tru từ chế độ người dùng sang chế độ ISP và yêu cầu khoảng 1ms.Điều này được theo sau bởi Kiểm tra ID, trong đó ID silicon của thiết bị được đọc để xác nhận mục tiêu chính xác.Tiếp theo, Xóa số lượng lớn Giai đoạn thay đổi trong các hướng dẫn xóa và áp dụng xung xóa 100ms, xóa tất cả dữ liệu hiện có trong các ô EEPROM.Các Chương trình Giai đoạn sau, trong đó các địa chỉ và dữ liệu được chuyển liên tục vào thiết bị, áp dụng các xung lập trình để định cấu hình các ô EEPROM.Mỗi địa chỉ phải được lập trình riêng lẻ, làm cho bước này tốn thời gian này tùy thuộc vào số lượng ô EEPROM trong thiết bị.

Sau khi lập trình hoàn tất, Xác minh Giai đoạn đảm bảo rằng dữ liệu đã được lưu trữ chính xác.Ở đây, đọc các xung được áp dụng cho các ô EEPROM và dữ liệu được truy xuất được so sánh với các giá trị dự kiến.Nếu sự khác biệt được tìm thấy, việc lập trình lại có thể là cần thiết.Cuối cùng, Thoát ISP Giai đoạn đảm bảo rằng các chân I/O chuyển trở lại chế độ người dùng, yêu cầu 1ms khác.Tổng thời gian lập trình hoặc xác minh bị ảnh hưởng bởi hai yếu tố chính: thời gian xung, cần thiết cho EEPROM erase, lập trình và đọc các hoạt động và thời gian thay đổi, phụ thuộc vào tần số TCK (đồng hồ thử nghiệm) và số lượng chu kỳ cần thiết để chuyển hướng dẫn, địa chỉ và dữ liệu.Do các thiết bị có khả năng ISP khác nhau có số lượng tế bào EEPROM khác nhau, cả tổng thời gian cố định và biến đổi là duy nhất cho mỗi thiết bị.Tổng thời gian ISP có thể được tính là một hàm của tần số TCK, số lượng thiết bị đích và kiến trúc EEPROM.

Các ứng dụng EPM7064STC100-7

Hệ thống nhúng

EPM7064STC100-7 được sử dụng rộng rãi trong các ứng dụng hệ thống nhúng, trong đó nó đóng vai trò là giải pháp logic lập trình linh hoạt để kiểm soát các thiết bị ngoại vi, tín hiệu xử lý khác nhau và thực hiện các giao thức tùy chỉnh.Khả năng giao diện của nó với các bộ vi điều khiển và cảm biến cho phép tối ưu hóa hiệu suất hệ thống trong khi vẫn duy trì dấu chân nhỏ gọn.Với hoạt động tốc độ cao và mức tiêu thụ năng lượng thấp, đây là một lựa chọn tuyệt vời cho các ứng dụng nhúng đòi hỏi độ tin cậy và hiệu quả.

Xử lý tín hiệu số (DSP)

Trong xử lý tín hiệu số, EPM7064STC100-7 đóng vai trò thực hiện các bộ lọc, điều chế tín hiệu và các chức năng toán học khác nhau.Tốc độ chuyển đổi nhanh và độ trễ lan truyền thấp của nó làm cho nó phù hợp để xử lý các tác vụ xử lý dữ liệu tần số cao, đảm bảo độ trễ tối thiểu trong chuyển đổi tín hiệu và thao tác.Nó thường được sử dụng trong xử lý âm thanh, viễn thông và hệ thống radar.

Truyền thông dữ liệu

EPM7064STC100-7 được sử dụng rộng rãi trong các hệ thống truyền thông dữ liệu và mạng do khả năng xử lý các hoạt động sử dụng nhiều logic như định tuyến dữ liệu, đệm và điều chỉnh lỗi.Các khả năng I/O có thể lập trình của nó cho phép nó thích ứng với các giao thức giao tiếp khác nhau, làm cho nó trở thành một thành phần có giá trị trong các công tắc Ethernet, bộ định tuyến và cơ sở hạ tầng viễn thông.Hỗ trợ của nó cho khả năng lập trình trong hệ thống (ISP) cũng cho phép cập nhật trường, cải thiện khả năng thích ứng trong môi trường mạng động.

Tự động hóa công nghiệp

Các ứng dụng công nghiệp đòi hỏi độ tin cậy, độ bền cao và mức tiêu thụ năng lượng thấp, làm cho EPM7064STC100-7 trở thành lựa chọn ưa thích cho Bộ điều khiển logic có thể lập trình (PLC), hệ thống điều khiển động cơ và thiết bị thử nghiệm tự động.Với khả năng lập trình trong hệ thống dựa trên JTAG, nó cung cấp khả năng tinh chỉnh các quy trình tự động hóa mà không cần phải loại bỏ hoặc thiết kế lại vật lý.Tính linh hoạt của nó trong khả năng tương thích điện áp cũng làm cho nó phù hợp để giao tiếp với một loạt các cảm biến và bộ truyền động được sử dụng trong các thiết lập công nghiệp.

EPM7064STC100-7 Các phần tương tự

Ưu điểm EPM7064STC100-7

Khả năng lập trình trong hệ thống (ISP)

Một trong những lợi thế lớn nhất của EPM7064STC100-7 là khả năng được lập trình lại trong khi vẫn được gắn trong hệ thống.Điều này giúp loại bỏ sự cần thiết phải loại bỏ chip để cập nhật, giảm thời gian bảo trì và cải thiện hiệu quả.Bạn có thể thực hiện các sửa đổi thiết kế mà không làm gián đoạn sản xuất, làm cho nó trở thành một giải pháp hiệu quả về chi phí cho các dự án dài hạn.

Hiệu suất tốc độ cao

Thiết bị hỗ trợ tần số hoạt động nội bộ cao lên tới 166,7 MHz, cho phép xử lý dữ liệu nhanh và thời gian phản hồi.Điều này làm cho nó lý tưởng cho các ứng dụng yêu cầu xử lý tín hiệu, điều khiển logic và giao diện tốc độ cao, đảm bảo hoạt động hệ thống mượt mà và đáng tin cậy hơn.

Hỗ trợ I/O đa năng

Với tối đa 68 chân I/O có thể định cấu hình và khả năng tương thích với nhiều mức điện áp (các tùy chọn 3,3V, 5V và dung nạp cho 2.5V, 3,3V và 5V), EPM7064STC100-7 cung cấp tính linh hoạt trong thiết kế hệ thống.Nó cho phép tích hợp liền mạch vào các mạch khác nhau và hỗ trợ môi trường điện áp hỗn hợp, giảm các vấn đề tương thích với các thành phần khác.

Hoạt động đáng tin cậy trên các môi trường

Được thiết kế để hoạt động trong phạm vi nhiệt độ từ 0 ° C đến 70 ° C, EPM7064STC100-7 đảm bảo hoạt động nhất quán và ổn định trong nhiều điều kiện khác nhau.Độ tin cậy này làm cho nó trở thành một lựa chọn ưa thích cho các ứng dụng cần sự ổn định môi trường, chẳng hạn như tự động hóa công nghiệp, viễn thông và hệ thống điều khiển nhúng.

EPM7064STC100-7 Sơ đồ pin ra

EPM7064STC100-7 là CPLD (thiết bị logic lập trình phức tạp) từ loạt Altera tựa Max 7000s, được đặt trong gói Quad phẳng mỏng 100 chân (TQFP-100).Loại gói này được thiết kế cho các ứng dụng gắn trên bề mặt, cung cấp sự cân bằng về mật độ pin cao và kích thước nhỏ gọn.Các Sơ đồ pin Theo một sơ đồ đánh số ngược chiều kim đồng hồ, với chân 1 nằm ở góc trên cùng bên trái của gói.Di chuyển ngược chiều kim đồng hồ, 25 chân đầu tiên chiếm bên trái, chân 26 đến 50 được định vị dọc theo cạnh dưới, chân 51 đến 75 tiếp tục dọc theo bên phải và các chân 76 đến 100 được phân phối dọc theo cạnh trên.Các Gói TQFP-100 Có các dây dẫn mỏng kéo dài ra ngoài từ cả bốn phía của thân phẳng, vuông.Thiết kế này tăng cường khả năng tương thích bề mặt trong khi duy trì khoảng cách pin đầy đủ để dễ dàng hàn và lắp ráp.Cao độ chì (khoảng cách giữa các chân liền kề) thường là 0,5mm, tối ưu hóa tính toàn vẹn tín hiệu trong khi giảm thiểu dấu chân tổng thể.

Nhà sản xuất EPM7064STC100-7

EPM7064STC100-7 là CPLD (thiết bị logic lập trình phức tạp) ban đầu được phát triển bởi Altera, một công ty bán dẫn được biết đến với các giải pháp logic có thể lập trình.Trong năm 2015, Intel Mua lại Altera, tích hợp các dòng sản phẩm FPGA và CPLD của mình vào Nhóm Giải pháp lập trình Intel (PSG).Kể từ đó, EPM7064STC100-7 đã được gắn nhãn hiệu theo Intel, mặc dù nó đã được đánh dấu là lỗi thời.Intel, với tư cách là nhà sản xuất, đã duy trì sự hỗ trợ kế thừa cho CPLD của MAX® 7000S Series, bao gồm cả mô hình này, trong khi dần dần chuyển trọng tâm của nó sang các công nghệ logic hiện đại và logic lập trình.

Phần kết luận

EPM7064STC100-7 tập hợp các chức năng phức tạp, hiệu suất nhanh và cập nhật dễ dàng trong một chip, chứng minh giá trị của nó trong các thiết lập kỹ thuật số đầy thách thức.Hướng dẫn này đã chỉ ra cách thức hoạt động của nó, những gì nó sử dụng và cách nó phù hợp với các hệ thống điện tử khác nhau.Nó giúp các thiết bị hoạt động trơn tru và hiệu quả, chứng minh rằng nó vẫn rất hữu ích cho nhiều ứng dụng.Hướng dẫn này cung cấp một cái nhìn rõ ràng về cách EPM7064STC100-7 có thể giúp cải thiện thiết kế điện tử và hoạt động hệ thống một cách hiệu quả.

Biểu dữ liệu PDF

EPM7064STC100-7 DATASHEETS:

Về chúng tôi

ALLELCO LIMITED

Đọc thêm

Yêu cầu nhanh chóng

Vui lòng gửi một yêu cầu, chúng tôi sẽ trả lời ngay lập tức.

Các câu hỏi thường gặp [FAQ]

1. Làm thế nào để độ trễ lan truyền 7.5NS của hiệu suất mạch tác động EPM7064STC100-7?

Độ trễ lan truyền 7,5NS đảm bảo xử lý tín hiệu độ trễ thấp, làm cho CPLD này phù hợp cho các ứng dụng tốc độ cao như xử lý tín hiệu số (DSP), hệ thống truyền thông và tự động hóa công nghiệp yêu cầu kiểm soát thời gian chính xác.

2. EPM7064STC100-7 có thể được lập trình bằng các công cụ phát triển hiện đại không?

Có, nó có thể được lập trình bằng phần mềm Quartus II của Intel (trước đây là Quartus Altera) cùng với một lập trình viên JTAG thích hợp.Tuy nhiên, hỗ trợ cho các CPLD cũ hơn như EPM7064STC100-7 có thể bị giới hạn trong các phiên bản Quartus mới hơn, vì vậy bạn có thể cần sử dụng các phiên bản cũ như Quartus II 13.0 SP1, vẫn hỗ trợ các thiết bị loạt MAX® 7000S.

3. EPM7064STC100-7 có hỗ trợ môi trường điện áp hỗn hợp không?

Có, nó hỗ trợ cả mức logic 3,3V và 5V, làm cho nó tương thích với một loạt các mạch kỹ thuật số.Tính linh hoạt này rất hữu ích cho các thành phần di sản 5V giao thoa với các hệ thống 3.3V hiện đại mà không cần thêm mạch thay đổi cấp độ.

4. Phương pháp tốt nhất để khắc phục sự cố thiết kế dựa trên EPM7064STC100-7 là gì?

Để khắc phục sự cố, bạn có thể sử dụng máy phân tích logic quartus Signtap II hoặc máy hiện sóng bên ngoài và máy phân tích logic để theo dõi tín hiệu.Nếu gỡ lỗi các vấn đề lập trình JTAG, hãy đảm bảo rằng các kết nối TDI, TDO, TCK và TMS là chính xác và bạn đã sử dụng một lập trình viên USB Blaster hoặc ByteBlasterMV tương thích.

5. Tôi có thể lập trình EPM7064STC100-7 mà không cần tháo nó ra khỏi bảng mạch của tôi không?

Đúng.Khả năng lập trình trong hệ thống 5.0V (ISP) thông qua JTAG (IEEE 1149.1) cho phép bạn lập trình lại thiết bị trong khi nó vẫn còn trong hệ thống.Điều này làm cho các bản cập nhật chương trình cơ sở, gỡ lỗi và kiểm tra hiệu quả hơn nhiều so với CPLD truyền thống.

Hướng dẫn đầy đủ về điện trở 10K: mã màu, ứng dụng và sử dụng mạch

trên 2025/03/10

Tụ điện so với pin: Cái nào tốt nhất cho nhu cầu năng lượng của bạn?

trên 2025/03/7

Bài viết phổ biến

-

Máy tính đặt hướng dẫn phức tạp: Làm thế nào họ thay đổi điện toán?

trên 8000/04/19 147782

-

Pinout và tính năng USB-C

trên 2000/04/19 112070

-

Sử dụng các nguyên thủy mô phỏng hợp nhất xilinx: Hướng dẫn toàn diện về thiết kế và mô phỏng FPGA

trên 1600/04/19 111352

-

Điện áp nguồn trong điện tử: Ý nghĩa của VCC, VDD, VEE, VSS và GND

trên 0400/04/19 83829

-

Hướng dẫn kết nối RJ45: Pinout, hệ thống dây điện, loại cáp và sử dụng

trên 1970/01/1 79642

-

Hướng dẫn cuối cùng về mã màu dây trong các hệ thống điện hiện đại

Cách hệ thống điện của chúng tôi sử dụng màu sắc không chỉ dành cho ngoại hình.Mỗi màu dây hiện chỉ ra một chức năng cụ thể, giúp xác định và xử lý các thành phần điện một cách dễ dàng hơn trong qu...trên 1970/01/1 67006

-

Hướng dẫn van thanh lọc: Chức năng, triệu chứng, xét nghiệm và thay thế cho hiệu suất động cơ tối ưu

Van thanh lọc là một phần quan trọng của hệ thống xe hơi giúp giữ cho không khí sạch bằng cách quản lý hơi nhiên liệu trước khi chúng có thể thoát vào khí quyển.Điều này không chỉ giúp môi trường b...trên 1970/01/1 63131

-

Chất lượng (Q) Yếu tố: Phương trình và ứng dụng

Yếu tố chất lượng, hoặc 'Q', rất quan trọng khi kiểm tra mức độ cuộn cảm và bộ cộng hưởng hoạt động tốt trong các hệ thống điện tử sử dụng tần số vô tuyến (RF).'Q' đo lường mức độ một mạch giảm thi...trên 1970/01/1 63067

-

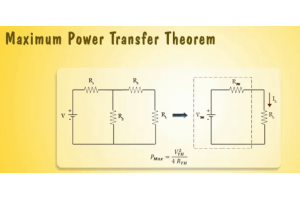

Đạt được hiệu suất cao nhất với Định lý Truyền công suất tối đa

Định lý truyền năng lượng tối đa giải thích cách năng lượng từ một nguồn, chẳng hạn như pin hoặc máy phát, chảy đến tải được kết nối.Nó cho thấy điều kiện chính xác trong đó tải nhận được nhiều năn...trên 1970/01/1 54097

-

Thông số kỹ thuật và khả năng tương thích của pin A23

Pin A23 là một pin nhỏ, hình xi lanh với điện áp cao.Cũng được gọi là 23A, 23AE hoặc MN21, nó chạy ở mức 12 volt và cao hơn nhiều so với pin AA hoặc AAA.Thiết kế đặc biệt của nó làm cho nó...trên 1970/01/1 52225