Hướng dẫn toàn diện về flip-flop Dual 74LS74

Bài viết này khám phá flip-flop 74LS74 D, một thành phần chính trong các hệ thống logic tuần tự.Nó nhấn mạnh chức năng có thể sử dụng được của IC, cấu hình pin, đặc điểm hoạt động và các ứng dụng đa dạng trong thiết bị điện tử kỹ thuật số.Bạn sẽ hiểu rõ hơn về vai trò của nó trong việc lưu trữ dữ liệu, đồng bộ hóa và thiết kế hệ thống tiên tiến.Danh mục

Tổng quan về flip-flop loại 74LS74

Các 74LS74 Mạch tích hợp, một flip-flop loại D được kích hoạt bởi cạnh kép, vượt trội trong việc duy trì và thay đổi dữ liệu trong các khung điện tử kỹ thuật số.Nó thể hiện khả năng thích ứng bằng cách tích hợp liền mạch với các mạch đa dạng như CMO, TTL và NMO, phản ánh sự phù hợp của nó đối với các cảnh quan điện tử khác nhau.Thiết kế của Flip-Flop cho phép nó điều chỉnh đầu ra dựa trên các mức logic được nắm bắt trong các điều kiện cài đặt đầu vào thấp, thể hiện sự thành thạo của nó trong việc phân tích và phản hồi các tín hiệu đầu vào.

Flip-flop này lão hóa và giữ lại đầu vào D trong suốt các giai đoạn chu kỳ đồng hồ.Nó đặc biệt bảo tồn trạng thái ở cạnh dương chính xác của mỗi xung đồng hồ.Độ chính xác này trong việc bắt giữ được trân trọng trong các hệ thống đồng bộ, trong đó thời gian nâng cao hiệu suất hệ thống.Việc thu thập dữ liệu đáng tin cậy này song song với độ chính xác theo yêu cầu của các công cụ chính xác trong các ứng dụng thời gian hoặc tần số, đòi hỏi tính nhất quán không ngừng.

Trên quy mô vĩ mô, người ta có thể thu hút sự tương đồng giữa chức năng của 74LS74 trong các hệ thống tinh vi và đồng bộ hóa cần thiết để phối hợp các hoạt động phức tạp.Ở đây, thời gian chính xác tạo điều kiện cho sự gắn kết và hợp lý hóa hiệu quả.Khả năng của Flip-flop để lưu trữ toàn vẹn dữ liệu một cách an toàn trong các chu kỳ giải thích tiện ích rộng rãi của nó trên các ứng dụng kỹ thuật số khác nhau, bao gồm lưu trữ dữ liệu trong bộ nhớ và môi trường máy tính.

Cấu hình pin 74LS74

|

Số pin số |

Biểu tượng pin |

Tên pin |

Sự miêu tả |

|

5, 9 |

1Q / 2Q |

Đầu ra |

Pin đầu ra của flip flop |

|

6, 8 |

1Q, (thanh) / 2Q (Bar) |

Đầu ra bổ sung |

Pin đầu ra đảo ngược của flip flop |

|

3, 11 |

1Clk / 2Clk |

Ghim đầu vào đồng hồ |

Những chân này phải được cung cấp xung đồng hồ cho lật

rơi phịch xuống |

|

1, 13 |

1ClR (Bar) / 2ClR (Bar) |

Xóa dữ liệu |

Đặt lại flip flop bằng cách xóa bộ nhớ của nó |

|

2, 12 |

1d / 2d |

Pin đầu vào dữ liệu |

Đầu vào của flip flop |

|

4, 10 |

1pre (thanh) / 2pre (bar) |

Đầu vào |

Một pin đầu vào khác cho flip flop.Cũng được gọi là một

Đặt pin |

|

7 |

VSS |

Đất |

Kết nối với mặt đất của hệ thống |

|

14 |

VDD/VCC |

Cung cấp điện áp |

Cung cấp năng lượng cho IC thường với 5V |

Các tính năng của 74LS74

• Hoạt động trên 2V đến 15V.

• Thời gian chuyển đổi tín hiệu nhanh 40ns.

• Hoạt động ở nhiệt độ từ 0 ° C đến 70 ° C.

• Đầu ra lên đến 8mA cho tải vừa phải.

• FLIP-FLIP-FLIP-FLOPS với đầu vào lưỡng cực và đầu ra kéo đẩy.

• Sử dụng công suất thấp, giảm EMI.

• Lý tưởng cho logic kỹ thuật số, lưu trữ dữ liệu và mạch tuần tự.

• Yêu cầu quản lý nhiệt tốt và nối đất thích hợp.

Ứng dụng của 74LS74

Đăng ký và thiết bị điều khiển thay đổi

Trong cảnh quan của các thanh ghi dịch chuyển, 74LS74 Hình dạng các chuỗi thời gian phức tạp được sử dụng để quản lý các luồng dữ liệu một cách hiệu quả.Bằng cách cung cấp truyền dữ liệu trơn tru và đồng bộ hóa, nó tăng cường chức năng mạch kỹ thuật số.Việc xử lý dữ liệu chính xác của nó tăng hiệu quả của việc chuyển đổi dữ liệu giữa các định dạng nối tiếp và song song.Thiết kế viễn thông thường xuyên phụ thuộc vào tính năng này để duy trì tính toàn vẹn dữ liệu và độ chính xác tín hiệu.

Bộ nhớ và mạch đệm

Trong kiến trúc bộ nhớ, 74LS74 không chỉ lưu trữ các bit dữ liệu mà đảm bảo tính nhất quán trong suốt các quy trình.Vai trò của nó như một bộ đệm đóng một phần trong việc thực hiện các tác vụ đầu vào-đầu ra trong khi bảo tồn tính toàn vẹn tín hiệu.Bộ đệm này rất quan trọng để ngăn chặn mất dữ liệu trong bối cảnh điện toán tốc độ cao.

Cơ chế chốt

Khả năng chốt của 74LS74 cho phép nó giữ lại thông tin an toàn, giữ tầm quan trọng trong các thiết bị lưu giữ nhà nước.Các cơ chế này đóng một vai trò trong việc bảo tồn các trạng thái hệ thống trong các chu kỳ năng lượng, cho phép các hệ thống khởi động lại chính xác.Trong các hệ thống điều khiển ô tô, duy trì một số trạng thái nhất định ngăn chặn sự cố và tăng cường an toàn.

Tích hợp trong tivi, máy tính và các công cụ mạng

Nó hỗ trợ trong việc thực hiện các hoạt động logic khác nhau để xử lý tín hiệu và hiển thị các tác vụ.Các công cụ mạng đạt được từ khả năng của chip để quản lý đồng thời nhiều đường dẫn dữ liệu, tăng thông lượng và giảm độ trễ.

Tương đương của 74LS74

• Hef40312b

Sử dụng IC 74LS74

74LS74 là một flip-flop loại D đa năng được biết đến với sự chuyển đổi nhanh và mức tiêu thụ năng lượng thấp, làm cho nó trở nên lý tưởng cho các tác vụ dữ liệu đồng bộ.Để đảm bảo hoạt động đúng, hãy bắt đầu bằng cách xác nhận rằng các chân VCC và GND được kết nối chính xác để cung cấp năng lượng ổn định.Các kết nối sức mạnh đáng tin cậy rất quan trọng để ngăn chặn các vấn đề gây ra bởi sự can thiệp hoặc bất thường trong nguồn cung.Đầu vào đồng hồ, nằm trên chân 3, kiểm soát thời gian thu thập dữ liệu.Khi đồng hồ nhận được tín hiệu cao, flip-flop sẽ thu thập dữ liệu.Tín hiệu đồng hồ có thể được lấy từ các bộ vi điều khiển (MCU) hoặc bộ đếm thời gian 555, tùy thuộc vào nhu cầu thời gian của mạch.

Chức năng đặt lại là một tính năng quan trọng khác của 74LS74.Áp dụng tín hiệu cao cho các đầu vào thiết lập lại xóa dữ liệu được lưu trữ, khả năng hữu ích trong các hệ thống yêu cầu xóa dữ liệu nhanh chóng.Vị trí thích hợp của các dòng thiết lập lại có thể tối ưu hóa các hoạt động và cải thiện hiệu suất hệ thống tổng thể.Để tăng cường hơn nữa độ tin cậy, điều quan trọng là phải giải quyết sự can thiệp tín hiệu tiềm năng thông qua các hoạt động nối đất hiệu quả và thiết kế mạch chiến lược.Các biện pháp này đảm bảo 74LS74 thực hiện một cách nhất quán, ngay cả trong các cấu hình phức tạp.Bạn có thể tối đa hóa hiệu quả và độ tin cậy của 74LS74 trong các thiết kế mạch của bạn.Hình dưới đây cho thấy mạch tích hợp flip-flop loại D 74LS74 được kết nối trong một cấu hình sử dụng đồng hồ của nó và đặt lại các đầu vào để quản lý trạng thái dữ liệu, thể hiện ứng dụng của nó trong mạch logic kỹ thuật số.

74LS74 D-TYPE FLIP-FLOP

|

Pre (Bar) |

CLR (Bar) |

CLK |

D |

Q. |

Q (Bar) |

|

L |

H |

X |

X |

H |

L |

|

H |

L |

X |

X |

L |

H |

|

L |

L |

X |

X |

H |

H |

|

H |

H |

H |

H |

L |

|

|

H |

H |

L |

L |

H |

|

|

H |

H |

L |

X |

Q₀ |

Q₀ (Bar) |

74LS74 Sơ đồ kết nối

Ưu điểm của d dép d dép

D Flip-flop cung cấp một lợi thế duy nhất trong thiết kế mạch kỹ thuật số bằng cách ngăn chặn các trạng thái đầu vào giống hệt nhau.Khía cạnh này đóng một vai trò trong việc ngăn chặn các cuộc đua tín hiệu và duy trì tính toàn vẹn của dữ liệu, đặc biệt là trong các hệ thống nơi thời gian và giải trình tự nâng cao hiệu suất.D Flip-flop đảm bảo tính nhất quán bằng cách chỉ bắt giữ một đầu vào cho mỗi chu kỳ đồng hồ, do đó làm mịn luồng dữ liệu và giảm thiểu các lỗi di chuyển tiềm năng.Đối với các nhà thiết kế, độ ổn định của luồng dữ liệu được đảm bảo được cung cấp bởi D Flip-Flops là một tính năng đáng tin cậy để quản lý các thách thức thời gian có thể làm tổn hại đến các hệ thống máy tính hoặc mạng.

Kiến trúc của flip-flops cung cấp tiện ích như các yếu tố độ trễ trong các sắp xếp mạch tinh vi.Sử dụng các cơ chế kiểm soát, chúng có thể được điều chỉnh để áp đặt sự chậm trễ cụ thể, quản lý truyền tín hiệu với độ chính xác.Thời gian có chủ ý này có lợi trong các kiến trúc đường ống yêu cầu dữ liệu để vượt qua nhiều giai đoạn có thể dự đoán được.Khả năng điều chỉnh độ trễ hỗ trợ giải quyết các vấn đề độ lệch đồng hồ, nếu không được giám sát, có thể cản trở hiệu suất mạch.

Gói cho 74LS74

Phần kết luận

Flip-flop loại D 74LS74 rất quan trọng để quản lý dữ liệu với độ chính xác trong thiết bị điện tử kỹ thuật số, đảm bảo đồng bộ hóa và lưu trữ đáng tin cậy trong nhiều ứng dụng.Tính linh hoạt và hiệu quả của nó trong việc xử lý và giữ lại dữ liệu làm cho nó trở thành một thành phần có giá trị trong việc tạo ra các hệ thống điện tử ổn định và chức năng.Với khả năng hoạt động trong các điều kiện khác nhau trong khi duy trì tính toàn vẹn tín hiệu, 74LS74 tiếp tục là một khối xây dựng trong việc thúc đẩy thiết kế và triển khai điện tử.Sự liên quan và khả năng thích ứng liên tục của nó trong bối cảnh công nghệ mới cho thấy tầm quan trọng của nó trong lĩnh vực này.

Về chúng tôi

ALLELCO LIMITED

Đọc thêm

Yêu cầu nhanh chóng

Vui lòng gửi một yêu cầu, chúng tôi sẽ trả lời ngay lập tức.

Các câu hỏi thường gặp [FAQ]

1. Có bao nhiêu flip-flops trong 7474?

Mạch tích hợp 7474 chứa hai flip flip loại D riêng biệt, mỗi flip có khả năng phát hiện các sự kiện kích hoạt cạnh.Thiết kế này tạo điều kiện cho việc lưu trữ và chuyển tiếp tín hiệu số hiệu quả, tinh chỉnh quy trình xử lý dữ liệu.Trình kích hoạt cạnh giúp tăng cường độ chính xác và độ tin cậy, một sự tinh tế thường được đánh giá cao thông qua kinh nghiệm thực hành trong các hệ thống phức tạp.

2. Tam giác có nghĩa là gì trên 74LS74?

Trong các thiết bị điện tử kỹ thuật số, tam giác đại diện cho đồng hồ được kích hoạt cạnh, căn chỉnh các hoạt động một cách liền mạch.Kết hợp với nó là một vòng tròn biểu thị tín hiệu hoạt động thấp, hỗ trợ trong các bài đọc mức độ logic điện tử chính xác.Những biểu tượng này đã được chứng minh trong việc ngăn chặn các thiết kế bị hiểu sai, một bài học ăn sâu vào tâm trí của các chuyên gia để ngăn chặn sự cố hệ thống.

3. Mục đích của 74LS74 là gì?

Chủ yếu, 74LS74 lưu trữ dữ liệu nhị phân, cho phép người dùng thực hiện các thay đổi chính xác.Khả năng thích ứng này đặc biệt thuận lợi đối với những người trong thiết kế hệ thống, trong đó sự đảm bảo về khả năng thích ứng và độ tin cậy của hệ thống được đánh giá cao, nhấn mạnh vai trò của IC trong các cảnh quan điện toán tinh vi.

4. D Flip Flop sử dụng 7474 là gì?

Được kích hoạt bởi các chuyển tiếp cạnh, một flip-flop trong 7474 sắp xếp các đầu ra Q với các ranh giới đầu vào.Kinh nghiệm thực tế cho thấy sự đóng góp của cơ chế này cho quản lý dữ liệu mạnh mẽ và tinh tế, để vận hành thành công các cơ sở hạ tầng kỹ thuật số phức tạp.

5. 74LS74N hoạt động như thế nào?

74LS74N tham gia vào các chân của nó, cho phép mỗi flip-flop hoạt động độc lập.Chức năng độc lập này được trân trọng trong các ứng dụng thực tế, trong đó một thiết kế mô -đun tăng cường độ tin cậy và khả năng thích ứng của hệ thống, một sở thích thường được lặp lại trong các kịch bản động.

6. 4 loại dép xỏ ngón?

Có bốn loại flip-flop chính: Latch/set-reset (SR), JK, T (chuyển đổi) và D (độ trễ hoặc dữ liệu).Mỗi người phục vụ một vai trò chuyên dụng trong các hệ thống xử lý dữ liệu, được thông báo bởi các ứng dụng thực tế khác nhau, nơi các quy trình kỹ thuật số tinh chỉnh giá trị.

7. Sự khác biệt giữa flip-flop D và T là gì?

D Dép xPTPRE Dữ liệu được căn chỉnh với tín hiệu đồng hồ, trong khi f-flops T dựa trên đầu vào T để chuyển đổi trạng thái.Sự khác biệt này phục vụ cho các ứng dụng yêu cầu thời gian và kiểm soát phức tạp, trong đó lựa chọn và tích hợp chu đáo có thể nâng cao hiệu suất hệ thống đáng kể.

8. Bảng chân lý d flip-flop là gì?

Một bảng chân lý lật D d có hiệu quả ngăn chặn sự khẳng định đồng thời các đầu vào S và R, sử dụng cấu hình SR được kiểm soát với biến tần để trình bày đầu vào D số ít.Trong thiết kế mạch thực tế, thiết lập này rất giỏi trong việc ngăn chặn điều kiện chủng tộc, một kỹ sư chướng ngại vật phổ biến cố gắng vượt qua.

9. Sự khác biệt giữa chốt và flip flop là gì?

FLIP-FLOPS được kích hoạt cạnh, không giống như các chốt phản ứng với các thay đổi mức đầu vào.Nắm bắt sự khác biệt này có lợi cho thiết kế mạch hiệu quả, vì nó đáp ứng nhu cầu chính xác theo thời gian độc đáo, một tham vọng dai dẳng để tối ưu hóa các hệ thống kỹ thuật số.

Mọi thứ bạn cần biết về bộ khuếch đại hoạt động LM358N

trên 2024/11/26

TL082 kép JFET OP-AMP: Pinout, Tương đương và Ứng dụng

trên 2024/11/26

Bài viết phổ biến

-

Máy tính đặt hướng dẫn phức tạp: Làm thế nào họ thay đổi điện toán?

trên 8000/04/18 147753

-

Pinout và tính năng USB-C

trên 2000/04/18 111925

-

Sử dụng các nguyên thủy mô phỏng hợp nhất xilinx: Hướng dẫn toàn diện về thiết kế và mô phỏng FPGA

trên 1600/04/18 111349

-

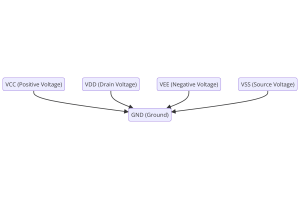

Điện áp nguồn trong điện tử: Ý nghĩa của VCC, VDD, VEE, VSS và GND

trên 0400/04/18 83714

-

Hướng dẫn kết nối RJ45: Pinout, hệ thống dây điện, loại cáp và sử dụng

trên 1970/01/1 79504

-

Hướng dẫn cuối cùng về mã màu dây trong các hệ thống điện hiện đại

Cách hệ thống điện của chúng tôi sử dụng màu sắc không chỉ dành cho ngoại hình.Mỗi màu dây hiện chỉ ra một chức năng cụ thể, giúp xác định và xử lý các thành phần điện một cách dễ dàng hơn trong qu...trên 1970/01/1 66872

-

Chất lượng (Q) Yếu tố: Phương trình và ứng dụng

Yếu tố chất lượng, hoặc 'Q', rất quan trọng khi kiểm tra mức độ cuộn cảm và bộ cộng hưởng hoạt động tốt trong các hệ thống điện tử sử dụng tần số vô tuyến (RF).'Q' đo lường mức độ một mạch giảm thi...trên 1970/01/1 63005

-

Hướng dẫn van thanh lọc: Chức năng, triệu chứng, xét nghiệm và thay thế cho hiệu suất động cơ tối ưu

Van thanh lọc là một phần quan trọng của hệ thống xe hơi giúp giữ cho không khí sạch bằng cách quản lý hơi nhiên liệu trước khi chúng có thể thoát vào khí quyển.Điều này không chỉ giúp môi trường b...trên 1970/01/1 62956

-

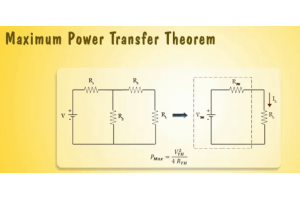

Đạt được hiệu suất cao nhất với Định lý Truyền công suất tối đa

Định lý truyền năng lượng tối đa giải thích cách năng lượng từ một nguồn, chẳng hạn như pin hoặc máy phát, chảy đến tải được kết nối.Nó cho thấy điều kiện chính xác trong đó tải nhận được nhiều năn...trên 1970/01/1 54078

-

Thông số kỹ thuật và khả năng tương thích của pin A23

Pin A23 là một pin nhỏ, hình xi lanh với điện áp cao.Cũng được gọi là 23A, 23AE hoặc MN21, nó chạy ở mức 12 volt và cao hơn nhiều so với pin AA hoặc AAA.Thiết kế đặc biệt của nó làm cho nó...trên 1970/01/1 52092