Hướng dẫn toàn diện về Testbenches: Công cụ và kỹ thuật để xác minh hệ thống kỹ thuật số

Hướng dẫn này khám phá TestBenches, một công cụ chính để xác thực phần mềm mô phỏng các điều kiện để kiểm tra đầu vào và xác minh đầu ra.TestBenches đóng một vai trò trong việc xác định lỗi sớm trong phát triển, cải thiện độ tin cậy của phần mềm.Với các ví dụ và hiểu biết thực tế, bài viết này nhấn mạnh việc sử dụng, kỹ thuật và tầm quan trọng của họ trong việc xây dựng các hệ thống kỹ thuật số mạnh mẽ, hiệu quả.Danh mục

Vai trò của TestBenches trong xác thực hệ thống kỹ thuật số

Testbench là một thành phần trong quá trình xác thực hệ thống kỹ thuật số.Nó không chỉ đơn thuần là một công cụ để tạo đầu vào và xác minh đầu ra, nó đóng vai trò là một khung toàn diện mô phỏng các điều kiện để đánh giá độ tin cậy, chức năng và hành vi của các hệ thống kỹ thuật số trước khi chúng được triển khai trong lĩnh vực này.Bằng cách tạo ra các môi trường được kiểm soát cho các hệ thống kiểm tra ứng suất với một loạt các kịch bản đầu vào, TestBenches giúp bạn xác định các lỗ hổng thiết kế tiềm năng sớm trong vòng đời phát triển, rất lâu trước khi hệ thống được đưa vào sản xuất.Việc phát hiện sớm các lỗi và lỗ hổng này là cần thiết để giảm các lỗi tốn kém, đảm bảo tuân thủ các thông số kỹ thuật hiệu suất và cải thiện độ tin cậy của hệ thống tổng thể.

Ngoài việc xác minh tính chính xác của các phản hồi của hệ thống, TestBenches đóng vai trò trong việc đánh giá các trường hợp cạnh, các vấn đề về thời gian và các cơ chế xử lý lỗi, đảm bảo hệ thống có thể hoạt động chính xác ngay cả trong điều kiện cực kỳ hoặc bất ngờ.Thông qua thử nghiệm và mô phỏng tự động, TestBenches đóng góp vào chất lượng phần mềm cao hơn, hiệu suất được cải thiện và chu kỳ phát triển ngắn hơn bằng cách cho phép thử nghiệm lặp mà không cần can thiệp thủ công.Họ phục vụ như một biện pháp bảo vệ chống lại những thất bại có thể xảy ra sau khi triển khai, đảm bảo sự mạnh mẽ và độ tin cậy của các hệ thống kỹ thuật số.

Các thành phần chính của Testbench và các chức năng của chúng

Để hiểu rõ hơn về cách hoạt động của TestBenches, điều quan trọng là khám phá các thành phần làm cho chúng hiệu quả.Một testbench được chế tạo tốt hoạt động bằng cách quản lý hai tác vụ cốt lõi: tạo đầu vào (kích thích) và xác minh đầu ra.Hãy kiểm tra từng thành phần một cách chi tiết.

Tạo ra kích thích

Tạo kích thích liên quan đến việc tạo ra một tập hợp các tín hiệu đầu vào mô phỏng các điều kiện để kiểm tra hành vi của hệ thống kỹ thuật số.Những đầu vào này cần phải vừa chính xác và thực tế để đảm bảo hệ thống phải chịu nhiều kịch bản mà nó có thể gặp phải trong thực tế.Hãy xem xét một mô -đun RAM cơ bản là một ví dụ.Testbench phải cung cấp các đầu vào cụ thể cho mô -đun và quan sát các đầu ra của nó để đảm bảo nó hoạt động như mong đợi.Các đầu vào khóa cho mô -đun RAM thường bao gồm:

• CLK (Đồng hồ): Điều khiển thời gian của hệ thống.

• addr (địa chỉ): Chỉ định vị trí dữ liệu nào để truy cập.

• WEN (Bật viết): Kiểm soát xem dữ liệu có được ghi vào bộ nhớ hay không.

• Dữ liệu: Thông tin thực tế được ghi vào mô -đun.

Đầu ra, được gọi là DataOut, thể hiện kết quả của các hoạt động nội bộ của mô -đun.Bằng cách cẩn thận viết kịch bản cách các đầu vào này được phân phối và giám sát DataOut, bạn có thể xác minh rằng hệ thống thực hiện chính xác trong các kịch bản khác nhau.Hãy nghĩ về việc tạo kích thích như thiết lập một kịch bản thử nghiệm trong phòng thí nghiệm.Giống như các nhà khoa học kiểm soát cẩn thận các điều kiện để quan sát các phản ứng hóa học, các nhà thiết kế kỹ thuật số tạo ra các đầu vào chính xác để quan sát cách một hệ thống phản ứng.

Xác minh đầu ra

Xác minh đầu ra là quá trình kiểm tra xem các đầu ra thực tế của hệ thống có phù hợp với kết quả dự kiến không.Bước này rất quan trọng trong việc bắt lỗi sớm trước khi chúng phát triển thành các vấn đề lớn hơn.Những người khác sử dụng xác minh đầu ra để xác nhận rằng hệ thống đáp ứng chức năng dự định của nó và thực hiện liên tục trong các điều kiện khác nhau.Xác minh đầu ra bao gồm cả kiểm tra tự động và thủ công.Ví dụ:

• Các công cụ xác minh tự động: Các công cụ như model và tứ hướng cho phép thử nghiệm tự động, trong đó các đầu ra của hệ thống được so sánh với kết quả dự kiến.Điều này tăng tốc quá trình xác minh và giảm lỗi.

• Xác minh thủ công (tùy chọn): Đối với các kịch bản phức tạp hơn, kiểm tra thủ công có thể cần thiết để đảm bảo rằng các trường hợp cạnh cụ thể được bảo hiểm.

Các công cụ và kỹ thuật để triển khai TestBench

Quartus: mô phỏng đầu vào/đầu ra trực quan

Quartus cung cấp một giao diện đồ họa sắp xếp trực quan các đầu vào và quan sát đầu ra.Phương pháp này có thể có lợi cho người mới bắt đầu hoặc cho các hệ thống đòi hỏi một cách tiếp cận trực quan, thực hành hơn.Bằng cách cho phép tương tác với một mô phỏng thông qua môi trường đồ họa, Quartus giúp làm sáng tỏ mối quan hệ giữa đầu vào và đầu ra, giúp dễ dàng hiểu được hệ thống kỹ thuật số hoạt động theo thời gian dễ dàng hơn.Một trong những thế mạnh chính của Quartus là nó là lý tưởng cho người mới bắt đầu.Giao diện trực quan, trực quan của nó cung cấp một cách đơn giản để xem các đầu vào ảnh hưởng đến đầu ra như thế nào mà không cần kiến thức kịch bản hoặc kịch bản mở rộng.Phản hồi mà nó cung cấp giúp nắm bắt hành vi của các mạch dễ dàng hơn, làm cho nó trở thành một công cụ hữu ích cho những người mới thiết kế hệ thống kỹ thuật số.Tuy nhiên, Quartus có những hạn chế của nó.Thiết lập mô phỏng trong Quartus có thể tốn thời gian, đặc biệt đối với các thiết kế phức tạp hơn.Công cụ này ít linh hoạt hơn so với các công cụ mô phỏng dựa trên kịch bản, có thể cung cấp nhiều tùy chọn tùy chỉnh và tự động hóa hơn.Để làm việc trên các hệ thống quy mô lớn hoặc chi tiết cao, sự thiếu linh hoạt này có thể đặt ra một thách thức.

Modelim: mô phỏng dựa trên văn bản sử dụng kịch bản

ModelIm có một cách tiếp cận khác nhau để mô phỏng bằng cách ưu tiên đầu vào dựa trên văn bản thông qua kịch bản.Tạo các kịch bản kiểm tra bằng các tập lệnh Verilog (.v) hoặc VHDL (.vhd), thay vì sắp xếp trực quan các đầu vào và đầu ra.Phương pháp này cung cấp độ chính xác và kiểm soát hơn.Thay vì dựa vào giao diện đồ họa, bạn xác định cách kiểm tra hệ thống thông qua các tập lệnh chi tiết, cho phép tùy chỉnh và tự động hóa lớn hơn trong quá trình mô phỏng.Một trong những điểm mạnh chính của ModelIM là sự linh hoạt mà nó cung cấp.Bằng cách sử dụng các tập lệnh, bạn có nhiều quyền kiểm soát hơn đối với các kịch bản kiểm tra, cho phép chúng tạo ra các mô phỏng phức tạp và chính xác.Khi một nhà thiết kế quen thuộc với cú pháp và quy trình làm việc, việc thiết lập mô phỏng có thể nhanh hơn nhiều so với sử dụng các công cụ đồ họa như Quartus.Khả năng tái sử dụng và sửa đổi các tập lệnh cũng làm tăng thêm hiệu quả của nó, đặc biệt là trong các dự án lớn hơn.Tuy nhiên, cách tiếp cận dựa trên văn bản của modelsim đi kèm với những hạn chế nhất định.Nó đòi hỏi một sự hiểu biết vững chắc về cú pháp Verilog hoặc VHDL, có thể đặt ra một thách thức cho những người mới bắt đầu không quen thuộc với các ngôn ngữ mô tả phần cứng.Do đó, ModelsIM có đường cong học tập dốc hơn so với các công cụ mô phỏng trực quan hơn.Người dùng mới có thể cảm thấy khó khăn khi bắt đầu, nhưng với thực tiễn, độ chính xác và tính linh hoạt được cung cấp bởi kịch bản có thể trở thành một tài sản có giá trị.

Kết nối lý thuyết và thực hành trong xác minh

Testbenches đóng vai trò là cầu nối giữa các thiết kế và ứng dụng lý thuyết bằng cách mô phỏng cách hệ thống kỹ thuật số sẽ hoạt động trong các điều kiện khác nhau, bao gồm các trường hợp cạnh và đầu vào bất ngờ.Trong thiết kế kỹ thuật số, thường rất khó để dự đoán một hệ thống sẽ thực hiện như thế nào trong thực tế chỉ dựa trên các mô hình lý thuyết.TestBenches thu hẹp khoảng cách này bằng cách cho phép bạn vượt ra ngoài các khái niệm thiết kế trừu tượng và đánh giá hành vi của hệ thống trong một môi trường được kiểm soát, mô phỏng.Một trong những lợi thế chính của việc sử dụng các công cụ mô phỏng trong TestBenches là phản hồi tức thì mà họ cung cấp trong quá trình gỡ lỗi.Các công cụ như Multisim hoặc ModelIM cung cấp các biểu diễn trực quan về hành vi hệ thống, cho thấy cách thay đổi đầu vào tác động đến đầu ra theo thời gian.Phản hồi này cho phép bạn xác định các vấn đề chính xác nhanh hơn, theo dõi các lỗi trở lại nguyên nhân gốc của chúng và điều chỉnh các thiết kế của chúng cho phù hợp.Ví dụ: nếu một hệ thống không đáp ứng các ràng buộc về thời gian hoặc thể hiện hành vi bất ngờ theo các chuỗi đầu vào nhất định, một testbench có thể làm nổi bật các lỗ hổng này ngay lập tức, rất lâu trước khi hệ thống được xây dựng vật lý.Bằng cách xác định các vấn đề sớm trong chu kỳ thiết kế, TestBenches làm giảm nhu cầu làm lại tốn kém và tạo mẫu vật lý, hợp lý hóa quá trình xác minh.Xác nhận giai đoạn đầu này giúp đảm bảo rằng các hệ thống kỹ thuật số vừa chính xác về mặt chức năng và kiên cường với các điều kiện, làm cho chúng đáng tin cậy hơn và giảm nguy cơ thất bại sau khi triển khai.Theo cách này, Testbenches hoạt động như một công cụ thực tế để biến các thiết kế lý thuyết thành mạnh mẽ.

Kiến trúc Testbench nâng cao

Testbenches nâng cao vượt xa thử nghiệm đầu vào-đầu ra đơn giản bằng cách kết hợp các thành phần bổ sung để quản lý các hệ thống phức tạp.Testbench tiêu chuẩn bao gồm ba phần chính: A Máy phát kích thích Để tạo tín hiệu đầu vào, một Thiết kế được thử nghiệm (DUT), đó là phần cứng thực tế đang được kiểm tra và Màn hình đầu ra Điều đó kiểm tra các đầu ra so với kết quả dự kiến.Các thành phần này làm việc cùng nhau để đảm bảo xác minh kỹ lưỡng và chính xác hơn về các thiết kế kỹ thuật số.

Cải thiện độ chính xác của TestBench liên quan đến việc sử dụng các kỹ thuật đảm bảo thiết kế thực hiện đáng tin cậy trong các kịch bản khác nhau. Kiểm tra ngẫu nhiên Giới thiệu các mẫu đầu vào không thể đoán trước để xác minh sự ổn định của hệ thống trong các điều kiện khác nhau. Kiểm tra trường hợp cạnh Tập trung vào các tình huống ranh giới trong đó hệ thống rất có thể gặp phải lỗi.Cuối cùng, Thử nghiệm hồi quy Liên quan đến các thử nghiệm chạy lại sau khi thay đổi để xác nhận rằng không có vấn đề mới nào được đưa ra, đảm bảo hệ thống vẫn nhất quán và không có lỗi theo thời gian.

Kịch bản testbenches

Để tạo ra các testbenches hiệu quả và đáng tin cậy trong Verilog hoặc VHDL, hãy làm theo các thực tiễn tốt nhất chính.Bắt đầu đơn giản, sau đó mở rộng bằng cách kiểm tra chức năng cơ bản trước và dần dần thêm các kịch bản phức tạp hơn.Sử dụng nhận xét và tài liệu để làm cho các tập lệnh của bạn dễ hiểu và duy trì hơn bằng cách giải thích rõ ràng từng phần.Cuối cùng, tự động hóa khi có thể tiết kiệm thời gian và giảm lỗi bằng cách sử dụng các vòng và chức năng để xử lý các tác vụ lặp đi lặp lại và các mẫu nhập.

Về chúng tôi

ALLELCO LIMITED

Đọc thêm

Yêu cầu nhanh chóng

Vui lòng gửi một yêu cầu, chúng tôi sẽ trả lời ngay lập tức.

Vòng lặp khóa pha kỹ thuật số (DPLL): Thiết kế, thành phần và hoạt động

trên 2025/01/7

Sự phát triển và tác động của kiến trúc RISC trong điện toán hiện đại

trên 2025/01/7

Bài viết phổ biến

-

Máy tính đặt hướng dẫn phức tạp: Làm thế nào họ thay đổi điện toán?

trên 8000/04/17 147712

-

Pinout và tính năng USB-C

trên 2000/04/17 111697

-

Sử dụng các nguyên thủy mô phỏng hợp nhất xilinx: Hướng dẫn toàn diện về thiết kế và mô phỏng FPGA

trên 1600/04/17 111318

-

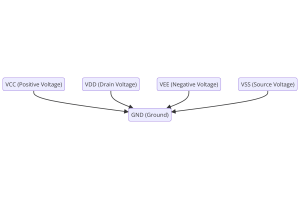

Điện áp nguồn trong điện tử: Ý nghĩa của VCC, VDD, VEE, VSS và GND

trên 0400/04/17 83593

-

Hướng dẫn kết nối RJ45: Pinout, hệ thống dây điện, loại cáp và sử dụng

trên 1970/01/1 79246

-

Hướng dẫn cuối cùng về mã màu dây trong các hệ thống điện hiện đại

Cách hệ thống điện của chúng tôi sử dụng màu sắc không chỉ dành cho ngoại hình.Mỗi màu dây hiện chỉ ra một chức năng cụ thể, giúp xác định và xử lý các thành phần điện một cách dễ dàng hơn trong qu...trên 1970/01/1 66763

-

Chất lượng (Q) Yếu tố: Phương trình và ứng dụng

Yếu tố chất lượng, hoặc 'Q', rất quan trọng khi kiểm tra mức độ cuộn cảm và bộ cộng hưởng hoạt động tốt trong các hệ thống điện tử sử dụng tần số vô tuyến (RF).'Q' đo lường mức độ một mạch giảm thi...trên 1970/01/1 62934

-

Hướng dẫn van thanh lọc: Chức năng, triệu chứng, xét nghiệm và thay thế cho hiệu suất động cơ tối ưu

Van thanh lọc là một phần quan trọng của hệ thống xe hơi giúp giữ cho không khí sạch bằng cách quản lý hơi nhiên liệu trước khi chúng có thể thoát vào khí quyển.Điều này không chỉ giúp môi trường b...trên 1970/01/1 62809

-

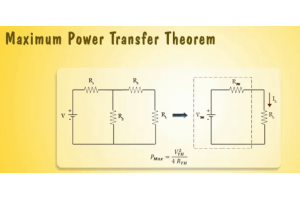

Đạt được hiệu suất cao nhất với Định lý Truyền công suất tối đa

Định lý truyền năng lượng tối đa giải thích cách năng lượng từ một nguồn, chẳng hạn như pin hoặc máy phát, chảy đến tải được kết nối.Nó cho thấy điều kiện chính xác trong đó tải nhận được nhiều năn...trên 1970/01/1 54027

-

Thông số kỹ thuật và khả năng tương thích của pin A23

Pin A23 là một pin nhỏ, hình xi lanh với điện áp cao.Cũng được gọi là 23A, 23AE hoặc MN21, nó chạy ở mức 12 volt và cao hơn nhiều so với pin AA hoặc AAA.Thiết kế đặc biệt của nó làm cho nó...trên 1970/01/1 51961