T kích hoạt Hướng dẫn kiến thức - ưu và nhược điểm, cách thức hoạt động, loại

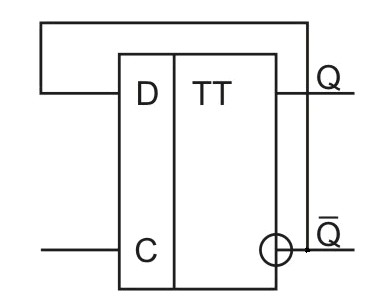

F-flip-flops tương tự như flip flip của JK.Bằng cách kết nối các đầu vào J và K, người ta có thể rút ra một flip-flop.Giống như một flip-flop D, nó chỉ có một đầu vào bên ngoài cùng với đồng hồ.

Danh mục

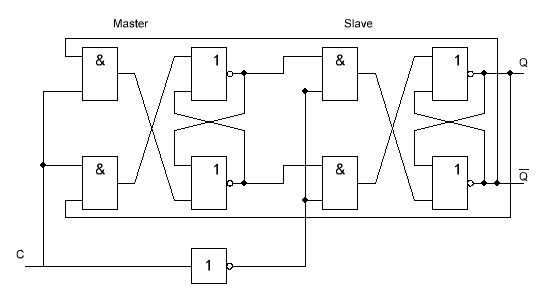

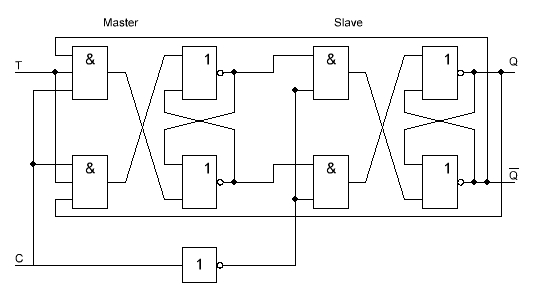

Làm thế nào TLIP-FLOPS hoạt động

dép xỏ ngón là các thiết bị đơn giản nhất trong Automata kỹ thuật số, thể hiện hai trạng thái ổn định.Một trạng thái giữ một giá trị của 1 1 và một trạng thái khác.Trạng thái của thiết bị và thông tin nhị phân được lưu trữ trong nó được xác định bởi các tín hiệu đầu ra: trực tiếp và nghịch đảo.Nếu một tiềm năng được đặt trên đầu ra trực tiếp tương ứng với đầu ra logic, thiết bị ở trạng thái kích hoạt đơn (tiềm năng của đầu ra nghịch đảo tương ứng với số 0 logic).Nếu không có tiềm năng trên đầu ra trực tiếp, thiết bị ở trạng thái không.

Các loại flip-flops

T-flip-flops chủ yếu có hai giống:

Trigger T không đồng bộ

Tương tự T đồng bộ

Cả hai loại của f-flip-flop hoạt động tương tự.Sự khác biệt duy nhất là trong quá trình chuyển đổi từ trạng thái này sang trạng thái khác.Loại không đồng bộ thực hiện trực tiếp quá trình chuyển đổi này, trong khi loại đồng bộ hoạt động dựa trên tín hiệu này.

Khi đánh giá một kịch bản trong đó đầu vào đồng hồ luôn cao (1), cần phải xem xét hai trạng thái tiềm năng của đầu vào chuyển đổi (t), cao (1) hoặc thấp (0).Hãy để chi tiết các kết quả cho từng trạng thái và các tương tác cổng logic liên quan.

Trường hợp 1: t = 0

- Điều kiện đầu ra: Ở đây, cả GATE1 và GATE2 đều và cổng được kết nối với T (đặt thành 0).

- Đầu ra GATE1 và GATE2: Vì một và cổng đầu ra 0 Khi bất kỳ đầu vào nào của nó là 0, các đầu ra của GATE1 và GATE2 sẽ luôn là 0, bất kể các đầu vào khác của chúng.

- GATE3/Q (N+1) Logic: GATE3 bị ảnh hưởng bởi đầu ra của GATE1.Khi GATE1 xuất ra 0, phương trình logic GATE3 đơn giản hóa thành không (0 hoặc không q), dẫn đến Q.

- GATE4/Q (n+1) 'logic: GATE4 tuân theo một mẫu tương tự, tạo ra không (0 hoặc q), đơn giản hóa để không q hoặc q'.

Tóm tắt trường hợp 1:

- Giả sử GATE1 = 0 và GATE2 = 0, và sử dụng đặc tính của và cổng (bất kỳ đầu vào nào của 0 đều có kết quả đầu ra là 0), hoạt động rất đơn giản:

- GATE3/Q (n+1) tính toán dưới dạng Q, duy trì trạng thái hiện tại.

- GATE4/Q (n+1) 'dẫn đến Q', bổ sung của trạng thái hiện tại.

Trường hợp 2: t = 1

- Điều kiện đầu ra: Khi T được đặt thành 1, các đầu vào của GATE1 và GATE2 hiện phản ánh các đầu ra của các hoạt động logic khác, ảnh hưởng đến đầu ra của chúng.

- Đầu ra GATE1 và GATE2: GATE1 kết nối trực tiếp với trạng thái hiện tại Q và GATE2 với không Q hoặc Q '.

- GATE4/Q (n+1) 'logic: Ở đây, phương trình đơn giản hóa vì các đầu vào của cổng và cổng là đối lập (Q và không Q), dẫn đến 0.

- GATE3/Q (n+1) logic: Mặt khác, Gate3 xử lý không phải Q hoặc Q ', xuất ra không (Q và 0), đơn giản hóa để không Q hoặc Q'.

Tóm tắt trường hợp 2:

- Thiết lập logic dẫn đến các tương tác thú vị:

- GATE1 = Q, GATE2 = Q ', ảnh hưởng đến các quá trình logic tiếp theo.

- GATE4/Q (n+1) 'trực tiếp tính toán là 0, vì và hoạt động giữa q và không q không thể đúng.

- GATE3/Q (n+1) sau đó tính toán dưới dạng q ', đó là chuyển đổi từ trạng thái trước khi t là 0.

T flip-flop bảng sự thật

|

CLK |

T |

Q (n+1) |

Tình trạng |

|

|

0 |

Q. |

Không thay đổi |

|

|

1 |

Q… |

Chuyển đổi |

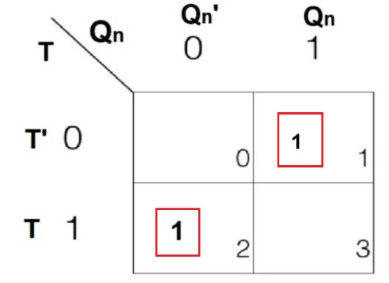

Chúng tôi sẽ sử dụng bảng sự thật này để biên dịch một bảng đặc trưng cho f-flop T.Trong bảng sự thật, bạn chỉ có thể thấy một đầu vào T và một đầu ra q (n+1).Tuy nhiên, trong bảng đặc trưng, bạn sẽ thấy hai đầu vào t và qn và một q (n+1) đầu ra.

Từ sơ đồ logic ở trên, rõ ràng Qn và Qn 'là hai đầu ra bổ sung, cũng đóng vai trò là đầu vào cho GATE3 và GATE4, do đó chúng tôi coi Qn (nghĩa là trạng thái hiện tại của Flip-flop) là đầu vào và Q (N+1) làm đầu ra cho trạng thái tiếp theo.

Sau khi hoàn thành bảng đặc trưng, chúng tôi sẽ xây dựng một bản đồ K 2 biến để rút ra phương trình đặc trưng.

|

T |

Qn |

Q (n+1) |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0

|

Từ bản đồ K, bạn có được hai cặp.Giải quyết cả hai, chúng tôi nhận được phương trình đặc trưng sau:

Q (n + 1) = tqn, + t hèqn = t xor qn

Ưu điểm của việc sử dụng flip-flops

Trong các mạch kỹ thuật số, T-Flip-flop cung cấp một số lợi ích đáng kể giúp đơn giản hóa chức năng và tích hợp của chúng:

- Đơn giản đầu vào duy nhất: T-flip-flop chỉ có một đầu vào, đơn giản hóa hoạt động của họ.Đầu vào đơn này có thể chuyển đổi giữa các trạng thái cao và thấp, cho phép nó tích hợp liền mạch vào các thiết kế mạch và dễ dàng kết nối với các mạch kỹ thuật số khác.

- Không có trạng thái không hợp lệ: T-flip-flops thiếu các quốc gia không hợp lệ, giúp ngăn chặn hành vi không thể đoán trước trong các hệ thống kỹ thuật số.Độ tin cậy này là rất quan trọng để duy trì hiệu suất hệ thống nhất quán.

- Giảm mức tiêu thụ điện: So với các flip-flop khác, f-flip-flop tiêu thụ ít năng lượng hơn.Hiệu quả năng lượng này có lợi cho việc mở rộng thời lượng pin của các thiết bị di động và giảm chi phí năng lượng của các hệ thống kỹ thuật số lớn.

- Hoạt động có thể sử dụng được: Giống như các flip-flop khác, T-flip-flop có hoạt động có thể sử dụng được, có nghĩa là chúng có thể giữ vô thời hạn trạng thái (0 hoặc 1) cho đến khi được kích hoạt bởi tín hiệu đầu vào.Đặc tính này rất cần thiết cho các ứng dụng yêu cầu lưu trữ dữ liệu đơn lẻ ổn định, dài hạn.

- Thực hiện dễ dàng: T-flip-flops có thể dễ dàng thực hiện bằng các cổng logic cơ bản.Sự đơn giản này làm cho chúng trở thành một lựa chọn khả thi về mặt kinh tế cho nhiều hệ thống kỹ thuật số, giúp giảm chi phí hệ thống tổng thể.

Hạn chế của flip-flops

Mặc dù có những lợi thế này, T-Flip-Flops cũng có một số hạn chế có thể ảnh hưởng đến sự phù hợp của chúng đối với các ứng dụng nhất định:

- Đầu ra đảo ngược: Đầu ra của flip-flops là trái ngược với đầu vào của nó, có thể làm phức tạp thiết kế của các mạch logic thời gian và làm cho thiết kế phức tạp hơn.Các nhà thiết kế cần xem xét điều này để đảm bảo hành vi mạch chính xác.

- Chức năng hạn chế: T-Flip-flops chỉ có thể lưu trữ một chút thông tin và không có khả năng thực hiện các hoạt động phức tạp như bổ sung hoặc nhân, hạn chế việc sử dụng chúng trong các tác vụ bộ nhớ cơ bản.

- Sự nhạy cảm với trục trặc: TLIP-flops có thể nhạy cảm với các trục trặc và nhiễu trên tín hiệu đầu vào, có khả năng gây ra những thay đổi trạng thái bất ngờ.Độ nhạy này có thể dẫn đến hành vi không thể đoán trước trong các hệ thống kỹ thuật số, đặc biệt là trong các môi trường có nhiễu điện tử cao.

- Độ trễ lan truyền: Giống như tất cả các flip-flop, T-flip-flop gặp phải sự chậm trễ lan truyền, có thể đưa ra các vấn đề về thời gian trong các hệ thống có các ràng buộc thời gian nghiêm ngặt.Những sự chậm trễ này phải được xem xét trong quá trình thiết kế hệ thống để tránh các lỗi thời gian và đảm bảo hoạt động đáng tin cậy.

Ứng dụng

Tlip-flops được sử dụng trong các ứng dụng trong thế giới thực khác nhau bao gồm:

- Phân chia tần số: D-flip-flops thường được sử dụng để giảm một nửa tần số của tín hiệu đồng hồ.Bằng cách chuyển đổi trạng thái của flip-flop với mỗi xung đồng hồ, chúng phân chia tần số của tín hiệu đầu vào một cách hiệu quả, khiến chúng trở nên lý tưởng cho thời gian chính xác và đồng hồ kỹ thuật số và bộ tổng hợp tần số.

- Tần số nhân đôi: Ngược lại, flip-flops cũng có thể được sử dụng để tăng gấp đôi tần số của tín hiệu đồng hồ, được gọi là tăng gấp đôi tần số.Điều này đạt được bằng cách định cấu hình flip-flop trong một thiết lập tạo ra tần số đầu ra gấp đôi tín hiệu đầu vào.

- Lưu trữ dữ liệu: T-Flip-flops có thể được sử dụng làm khối xây dựng cơ bản để lưu trữ các bit dữ liệu đơn lẻ, trong đó dữ liệu cần được lưu tạm thời để xử lý hoặc truyền thêm.Điều này làm cho chúng rất hữu ích trong các ứng dụng như thanh ghi ca và thiết bị lưu trữ.

- QUẢN LỰC: Một ứng dụng quan trọng khác của flip-flops là tạo ra các bộ đếm nhị phân.Chúng có thể được kết nối với các cổng logic kỹ thuật số khác để xây dựng các bộ đếm có thể tăng hoặc giảm đếm dựa trên các yêu cầu thiết kế.